2

SPP-A1070/A1071

TABLE OF CONTENTS

1. SERVICING NOTES ................................................ 2

2. GENERAL ................................................................... 4

3. DISASSEMBLY

3-1. Disassembly Flow ........................................................... 5

3-2. H/S Rear Assy ................................................................. 5

3-3. H/S FRT Assy.................................................................. 6

3-4. HAND MAIN Board....................................................... 6

3-5. Base Bottom .................................................................... 7

3-6. BASE MAIN Board ........................................................ 7

4. TEST MODE.............................................................. 8

5. DIAGRAMS

5-1. Block Diagram – BASE UNIT Section – ...................... 11

5-2. Block Diagram – HANDSET Section – ........................ 12

5-3. Note for Printed Wiring Boards and

Schematic Diagrams ....................................................... 13

5-4. Printed Wiring Board – BASE MAIN Board –............. 14

5-5. Schematic Diagram – BASE MAIN Board –................ 15

5-6. Printed Wiring Board – BASE KEY Board – ............... 16

5-7. Schematic Diagram – BASE KEY Board – .................. 16

5-8. IC Pin Function Description ........................................... 17

5-9. Printed Wiring Board – HAND MAIN Board – ............ 18

5-10. Schematic Diagram – HAND MAIN Board – .............. 19

6. EXPLODED VIEWS

6-1. Hand Set Section ............................................................. 20

6-2. Base Set Section.............................................................. 20

7. ELECTRICAL PARTS LIST ............................... 21

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK 0OR DOTTED

LINE WITH MARK 0ON THE SCHEMATIC DIAGRAMS

AND IN THE PARTS LIST ARE CRITICAL TO SAFE

OPERATION. REPLACE THESE COMPONENTS WITH

SONY PARTS WHOSE PART NUMBERS APPEAR AS

SHOWN IN THIS MANUAL OR IN SUPPLEMENTS PUB-

LISHED BY SONY.

ATTENTION AU COMPOSANT AYANT RAPPORT

À LA SÉCURITÉ!

LES COMPOSANTS IDENTIFIÉS PAR UNE MARQUE 0

SUR LES DIAGRAMMES SCHÉMATIQUES ET LA LISTE

DES PIÈCES SONT CRITIQUES POUR LA SÉCURITÉ

DE FONCTIONNEMENT. NE REMPLACER CES COM-

POSANTS QUE PAR DES PIÈCES SONY DONT LES

NUMÉROS SONT DONNÉS DANS CE MANUEL OU

DANS LES SUPPLÉMENTS PUBLIÉS PAR SONY.

Notes on chip component replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

NOTE FOR REPLACEMENT OF THE EEPROM

The ID cord is written in the EEPROM.

When replacing the EEPROM, U6 on the BASE MAIN board and

U4 on HAND MAIN board should be replaced together as a pair.

(Parts No. X-3381-019-1)

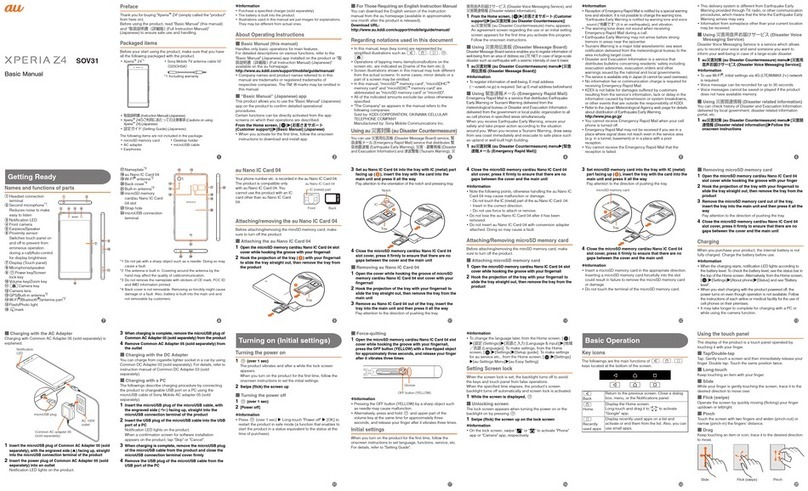

PRIOR CHECK FOR SERVICING

This set can rewrite the ID number of handset to the ID number of

base unit in the test mode even their serial numbers are different.

You can find which is wrong, handset or base unit with this

function.

Note: A normal set is needed for this test.

Define A as the normal set and B as the faulty set.

Disconnect their power.

Procedure:

1. Press the [PGM] key.

2. Select the “DIAL MODE” menu by pressing v or V keys.

3. Press the key sequence [SELECT], [2], [1], [0], [4].

4. When enter the test mode, happy tone is emitted, and the LCD

displays as shown below.

5. While pressing the [HANDSET LOCATOR] key of the base

unitA, turn the power on, then release and press it again within

2 seconds to enter the test mode.

6. When enter the test mode, the [LINE] LED blinks slowly .

7. Disconnect the power of the handset B, then connect the power

again.

8. Disconnect the power of the base unitA, then connect the power

again.

9. Cradle the handset B on the base unit A to charge the battery

of handset B for about 1 minute.

10. Press the [TALK] key of the handset B and join the base unit

A.

11. When joining is successful, the handset B is normal. But when

it fails, charge the battery of the handset B again.

12. Next, repeat the step 1 to step 9 with the handset A and base

unit B

13. When joining is successful with handset A and base unit B,

base unit B is normal and handset B is faulty.

SECTION 1

SERVICING NOTES