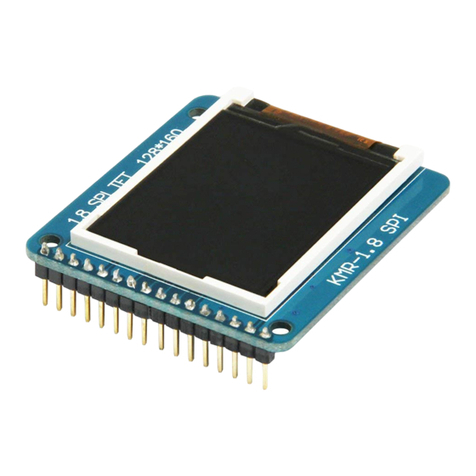

Sitronix ST7038

Dot MatrixLCD Controller/Driver

Ver1.11/612007/01/25

FEATURES

l5 x 8dot matrixpossible

lSupportlowvoltage single poweroperation:

ØVDD, VDD2: 1.8to3.3V(typical)

lLCD Voltage Operation Range (V0/Vout)

ØProgrammable V0: 3 to 7V(V0)

ØExternalpowerapplied: Max. 12V(Vout)

lInterface

Ø6800-4bit / 8bitinterface

Ø8080-4bit / 8bitinterface

Ø3-line serialinterface

Ø4-line serialinterface

ØI

2

C interface

lSupportdisplay mode:

Ø8-COM x100-SEGand 80ICON

Ø16-COM x100-SEGand 80 ICON

Ø24-COM x80-SEGand 80 ICON

l10,240-bitCharacterGeneratorROM

(CGROM)stores 256characterfonts

l64 x 8-bitCharacterGeneratorRAM

(CGRAM)

l80 x 8-bitDisplayRAM(80 characters max.)

l16 x 5 bitICONRAM

lVariable instruction functions:

cleardisplay,returnhome, displayON/OFF,

cursorON/OFF,characterblink,cursorshift,

displayshift, doubleheightfont, ICONcontrol

and charactergeneration RAM

lResetcircuitthrough anexternal resetpin

lInternal oscillatororexternal clock

lBuilt-inlowpowerconsumption voltage

booster,regulatorand followercircuit

lBuilt-inhigh-accuracyvoltage regulator:

ØProgrammable outputrange: 3~7V

lCOM/SEGdirection selectable byinstruction

lSelectable CGRAM/CGROMsize

lPackage Type:COG

GENERALDESCRIPTION

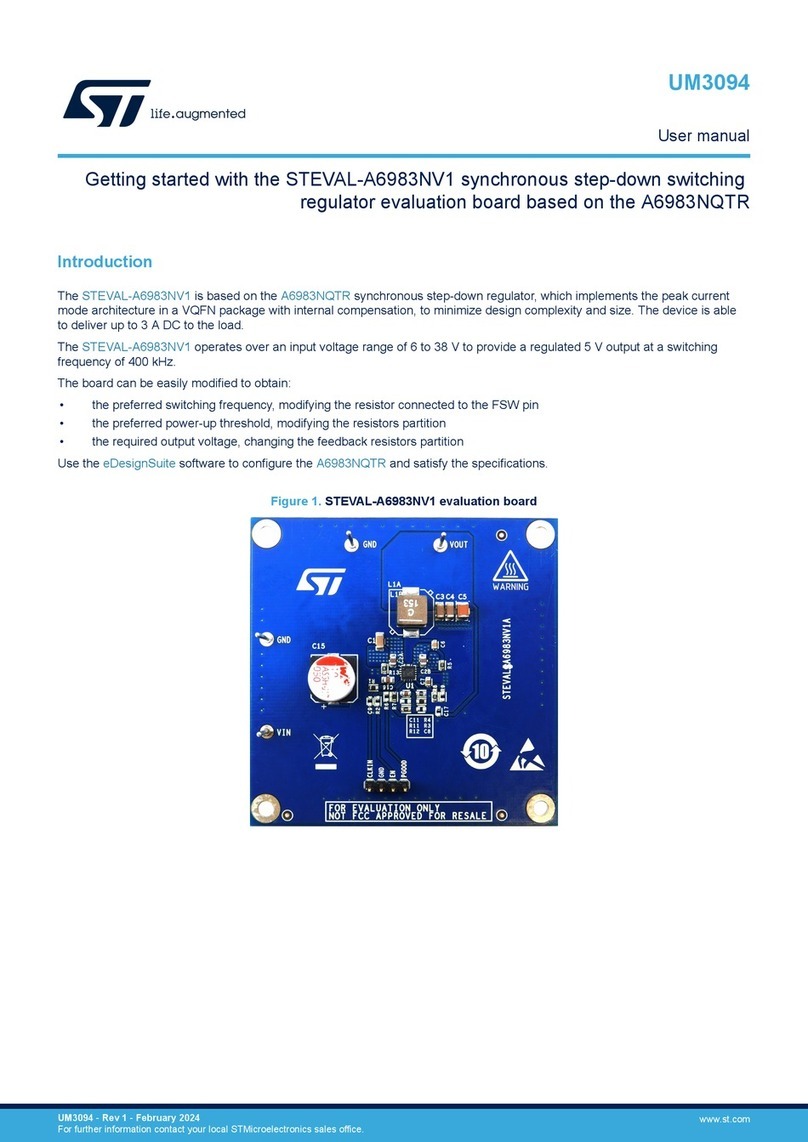

ST7038 dot-matrixliquid crystal displaycontrollercan

displayalphanumeric,Japanesekanacharactersand

symbols.It can be configuredtodriveadot-matrixliquid

crystaldisplayunderthecontrol ofamicroprocessorwith

4/8-bit6800-seriesor8080-series,3/4-lineserialorfastI2C

interface.Sinceallthefunctions(suchasdisplayRAM,

charactergeneratorROM/RAMand liquidcrystaldriver)

required fordrivingadot-matrixliquidcrystaldisplayare

internallyembedded in thischip,aminimal systemcan be

usedwiththiscontroller/driver.

The CharacterGeneratorROM ofST7038 has256 5x8dot

cellsand stores256 differentcharacter fonts(5x8dot).

ST7038 issuitable forlowvoltage supply(1.8Vto3.3V) and

is perfectlysuitableforanyportableproductwhichisdriven

bythe batteryandrequireslowpower consumption.

The displayresolutionofST7038 dot-matrixLCD drivercan

be either1-linex20 characters,2-line x20 charactersor

3-linex16 characterswith80-bit ICON.

ST7038 works alone without extracascaded drivers.

ProductName Charactergenerator ROMSize SupportCharacter

ST7038-0B256 English/ Europe/ Japan

ST7038

6800-4bit/ 8bitinterface

8080-4bit/ 8bitinterface

3-line/4-lineserial interface

(withoutI2Cinterface)

ST7038iI

2

Cinterface