Obsolete Product(s) - Obsolete Product(s)

L6917B

8/33

Device Description

The device is an integrated circuit realized in BCD technology. It provides complete control logicand protections

for a high performance dual-phase step-down DC-DC converter optimized for microprocessor power supply. It

is designed to drive N Channel MOSFETs in a dual-phase synchronous-rectified buck topology. A 180 deg

phase shift is provided between the two phases allowing reduction in the input capacitor current ripple, reducing

also the size and the losses. The output voltage of the converter can be precisely regulated, programming the

VID pins, from 1.100V to 1.850V with 25mV binary steps, with a maximum tolerance of ±0.8% over temperature

and line voltage variations. The device provides an average current-mode control with fast transient response.

It includesa 300kHz free-running oscillator adjustable up to 600kHz. The error amplifier features a 15V/

µ

s slew

rate that permits high converter bandwidth for fast transient performances. Current information is read across

the lower mosfets r

DSON

or across a sense resistor in fully differential mode. The current information corrects

the PWM output in order to equalize the average current carried by each phase. Current sharing between the

two phases is then limited at ±10% over static and dynamic conditions. The device protects against over-cur-

rent, with an OC threshold for each phase, entering in constant current mode. Since the current is read across

the low side mosfets, the constant current keeps constant the bottom of the inductors current triangular wave-

form. When an under voltage is detected the device latches and the FAULT pin is driven high. The device per-

forms also over voltage protection that disable immediately the device turning ON the lower driver and driving

high the FAULT pin.

Oscillator

Thedevice hasbeen designedinorder tooperate aneach phaseat thesame switching frequencyofthe internal

oscillator. So, input and output resulting frequency is doubled.

The switching frequency is internally fixed to 300kHz. The internal oscillator generates the triangular waveform

for the PWM charging and discharging with a constant current an internal capacitor. The current delivered to the

oscillator is typically 25

µ

A and may be varied using an external resistor (R

OSC

) connected between OSC pin

and GND or Vcc. Since the OSC pin is maintained at fixed voltage (typ). 1.235V, the frequency is varied pro-

portionally to the current sunk (forced) from (into) the pin considering the internal gain of 12KHz/

µ

A.

In particular connecting it to GND the frequency is increased (current is sunk from the pin), while connecting ROSC

to Vcc=12V the frequency is reduced (current is forced into the pin), according to the following relationships:

Note that forcing a 25

µ

A current into this pin, the device stops switching because no current is delivered to the

oscillator.

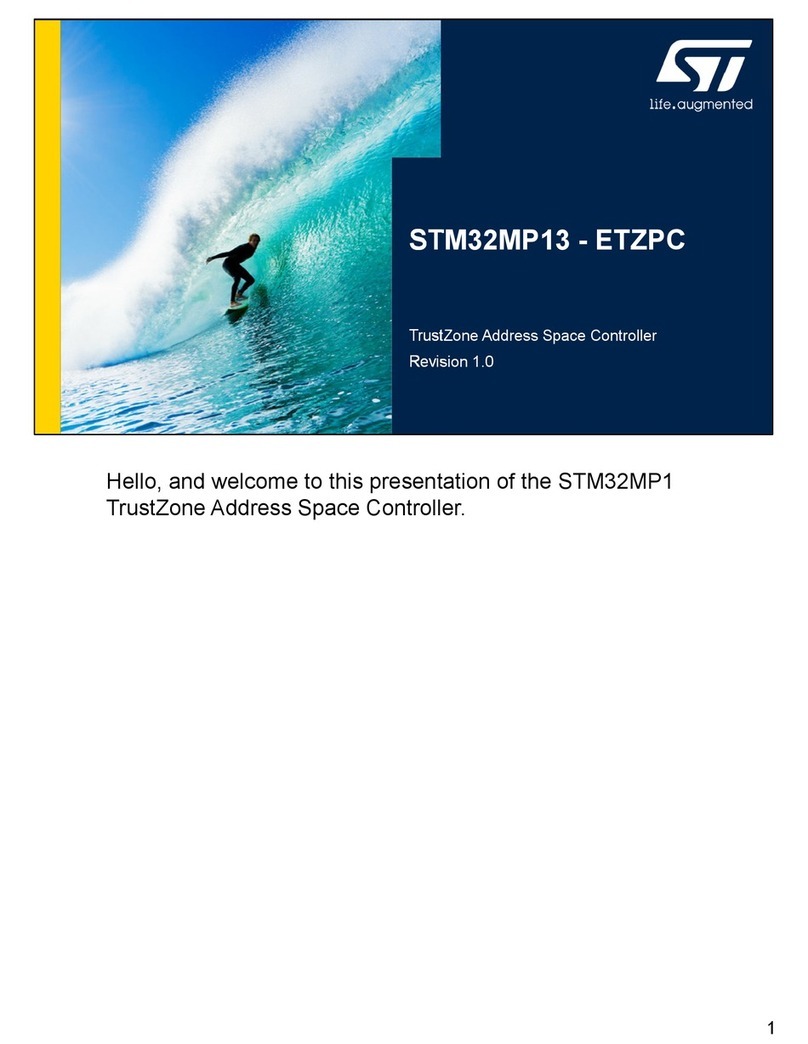

Figure 1. ROSC vs. Switching Frequency

ROSCvs.GND: fS300kHz 1.237

ROSC KΩ()

------------------------------ 12kHz

µA

-----------⋅+300kHz 14.82 106

⋅

ROSC KΩ()

------------------------------+==

R

OSCvs.12V: fS300kHz 12 1.237

–

ROSC KΩ()

------------------------------ 12kHz

µA

-----------

⋅–300kHz 12.918 107

⋅

ROSC KΩ()

--------------------------------–==

0

1000

2000

3000

4000

5000

6000

7000

0 100 200 300

Frequency (KHz)

Rosc(KΩ) vs. 12V

0

100

200

300

400

500

600

700

800

900

1000

300 400 500 600 700 800 900 1000

Frequency (KHz)

Rosc(KΩ) vs. GND

Obsolete Product(s) - Obsolete Product(s)