Terasic AHA-HSMC User manual

Table of contents

Other Terasic Computer Hardware manuals

Terasic

Terasic XTS User manual

Terasic

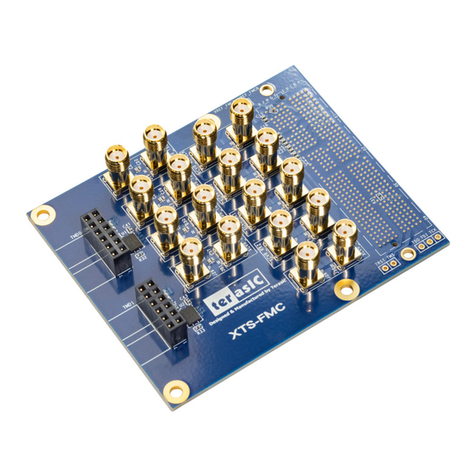

Terasic XTS-FMC User manual

Terasic

Terasic Mercury A2700 User manual

Terasic

Terasic THDB-H2S User manual

Terasic

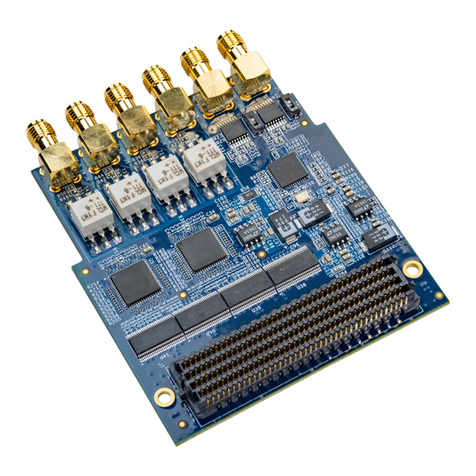

Terasic ADC-FMC User manual

Terasic

Terasic DE10-Agiles User manual

Terasic

Terasic RFS2 User manual

Terasic

Terasic DE0-Nano-SoC Guide

Terasic

Terasic PCA3 User manual

Terasic

Terasic NET-FMC User manual

Popular Computer Hardware manuals by other brands

Promise

Promise VTRAK 15100 quick start guide

Contec

Contec Flexlan PC Card FX-DS-110 user guide

Corsair

Corsair H80i Quick start quide

Ebmpapst

Ebmpapst D3G133-LV05-31 operating instructions

ARTESYN EMBEDDED TECHNOLOGIES

ARTESYN EMBEDDED TECHNOLOGIES SharpStreamer Pro PCIE-7210 Assembly, Installation and Use

Multitech

Multitech MT5600SMI brochure

IPEX

IPEX Genesis F3 Operator's guide

Power bass

Power bass PB-DBR1 owner's manual

Multitech

Multitech MultiModem ISI5634UPCI-4 quick start guide

Data Video

Data Video KMU-100 instruction manual

Matrox

Matrox RT.X100 Xtreme Installation and user guide

Enterasys

Enterasys RoamAbout RBTBG-AW Installations and specifications