Open Access

Introduction

1-4 ARM Development Board (ARM7TDMI Version)

Hardware Reference Guide

ARM DUI 0017C

1.4 Glossary Some of the terms used in this manual may be unfamiliar to you. This section explains some

of the more important ones.

ARM7TDMI The ARM7TDMI test chip is an example of an ARM processor

macrocellthatissuitableforuseon theARMDevelopmentCard.

See the

ARM7TDMI Data Sheet

(ARM DDI 0029) for more

information.

CPLD A

complex programmable logic device

(

CPLD

) is usually

a collection of PAL-type devices in a single package.

The AMD MACH device is an example of a CPLD.

EmbeddedICE This is the additional hardware that is provided by debuggable

ARM processors to aid debugging. The EmbeddedICE

macrocell is fully described in the

ARM7TDMI Data Sheet

(ARM

DDI 0029). The EmbeddedICE macrocell is controlled via the

JTAGtest access port, using an EmbeddedICE interface. This is

an extra piece of hardware that allows software tools to debug

code running on a target processor.

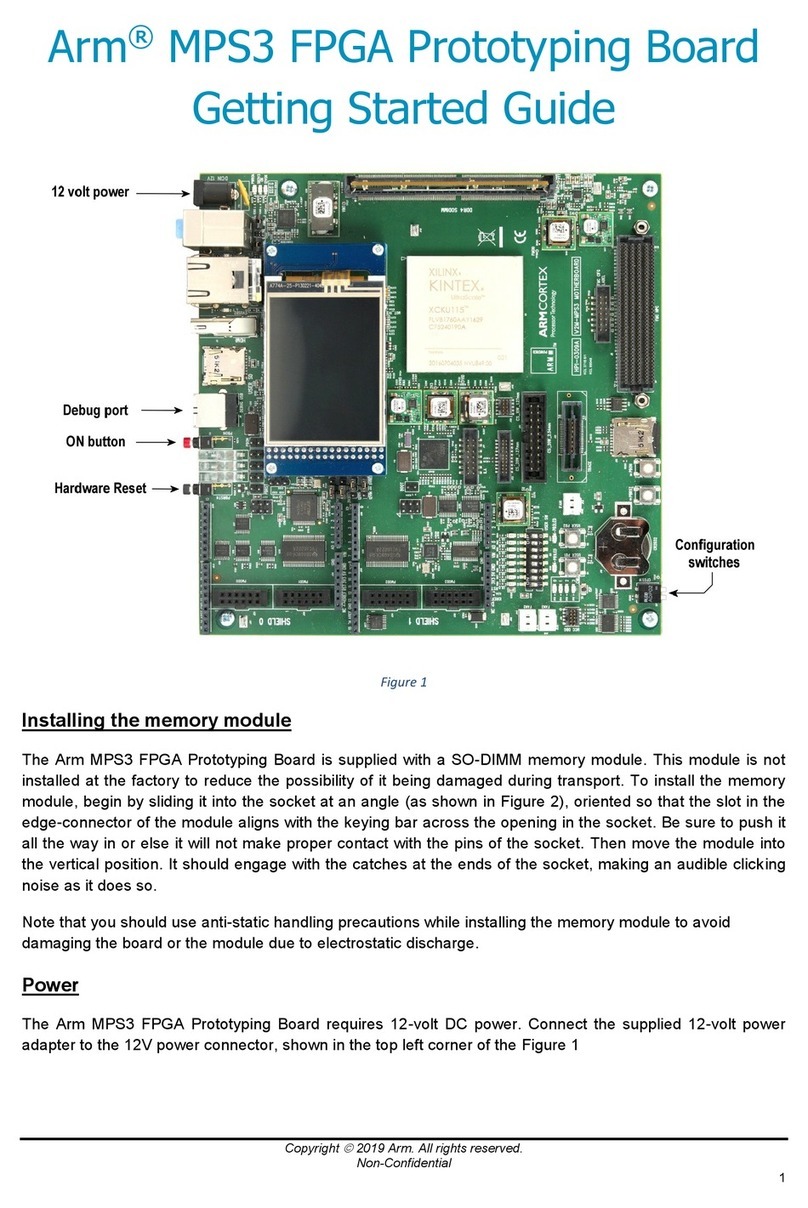

FPGA A

field-programmable gate array

(

FPGA

) is a type of

programmable logic device

(

PLD

). The ARM Development Card

is fittedwith one FPGA manufactured byXilinx. You can change

the functionality of thisdevice if the appropriate design tools are

available. Xilinx sells an appropriate tool set which interfaces to

a variety of front-end systems which may be based on

schematics or hardware description languages such as VHDL.

See also

LCA

.

ICE An

in-circuit emulator

(

ICE

), is a device that aids debugging of

hardware and software. ARM debuggable processors such as

the ARM7TDMI have extra hardware called

EmbeddedICE

to

assist this process.

JTAG This is a serial-like test port provided on many large silicon chips

such as the ARM7TDMI.

LCA A

logic cell array

(

LCA

) is a type of

programmable logic device

(

PLD

) also known as a

field-programmable gate array

(

FPGA

).

MACH A MACH device is a example of a

complex programmable logic

device

(

CPLD

). The ARM Development Card uses a number of

MACH210 and MACH230 devices. Based on electrically

erasable (

EE

) technology, they are reprogrammable. Using

appropriate software (such as PALASM), the function of these

devices may be changed by reprogramming in a standard

programmer.

NISA

NISA

(

not-ISA

) is ARM’s descriptionof the bus thatconnects the

Advanced System Bus

(

ASB

) to some standard peripheral

devices such as the serial/parallel ports and PC card controller.

It is a subset of the

Industry Standard Architecture

(

ISA

) bus

found in most IBM compatible PCs.

hrg.book Page 4 Wednesday, July 22, 1998 9:18 AM