SoC-FPGA Design Guide [DE0-Nano-SoC Edition]

03/10/2018 P a g e | 5

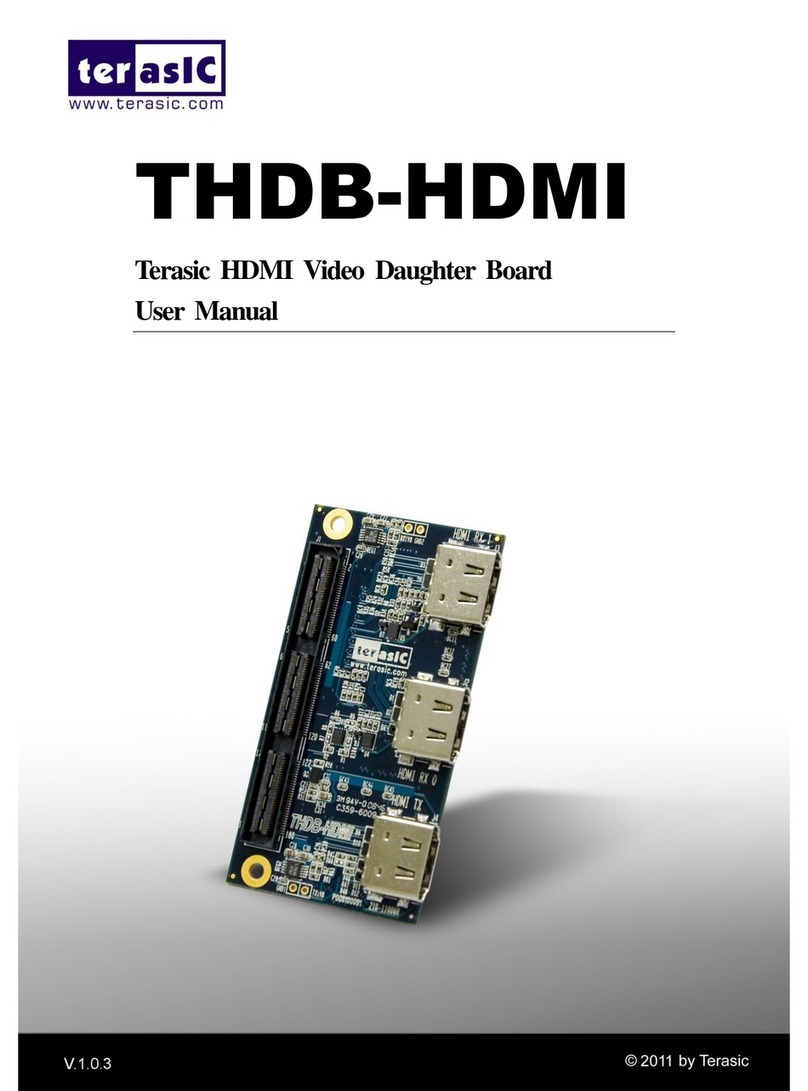

Figure 6-1. Terasic DE0-Nano-SoC Board [1] ........................................................................................................ 12

Figure 6-2. Block Diagram of the DE0-Nano-SoC Board [1] ................................................................................. 13

Figure 6-3. Back [1] .............................................................................................................................................. 14

Figure 6-4. Front [1] ............................................................................................................................................. 14

Figure 7-1. Altera SoC FPGA Device Block Diagram [2, pp. 1-1]........................................................................... 15

Figure 7-2. HPS Block Diagram [2, pp. 1-3] .......................................................................................................... 17

Figure 7-3. HPS Address Space Relaons [2, pp. 1-14] ........................................................................................ 20

Figure 7-4. Simplied HPS Boot Flow [2, pp. A-3] ................................................................................................ 23

Figure 7-5. Independent FPGA Conguraon and HPS Boong [2, pp. A-2]........................................................ 24

Figure 7-6. FPGA Conguraon before HPS Boong (HPS boots from FPGA) [2, pp. A-2]................................... 24

Figure 7-7. HPS Boots and Performs FPGA Conguraon [2, pp. A-3]................................................................. 25

Figure 7-8. HPS Boot Flows [2, pp. A-3] ............................................................................................................... 25

Figure 8-1. Project Folder Structure..................................................................................................................... 29

Figure 9-1. Basic Nios II System with on-chip memory and JTAG UART .............................................................. 31

Figure 9-2. Adding LEDs to the System ................................................................................................................ 31

Figure 9-3. HPS Component Parameters ............................................................................................................. 32

Figure 9-4. HPS_KEY_N & HPS_LED on DE0-Nano-SoC Schematic. Note that the schematic uses “HPS_KEY”

instead of “HPS_KEY_N” as the name of the signal. This is a mistake, as the button is active-low, so the “_N” in

the name is warranted for clarity. ....................................................................................................................... 32

Figure 9-5. HPS_KEY_N & HPS_LED on Qsys Peripheral Pins Tab ........................................................................ 33

Figure 9-6. Using Pin G21 for SPI.......................................................................................................................... 33

Figure 9-7. Ethernet MAC configuration.............................................................................................................. 34

Figure 9-8. SD/MMC configuration ...................................................................................................................... 34

Figure 9-9. UART configuration............................................................................................................................ 34

Figure 9-10. Exported peripheral pins ................................................................................................................. 34

Figure 9-11. USB, SPI, and I2C peripheral pin configurations............................................................................... 35

Figure 9-12. Adding the "Standalone" HPS to the System................................................................................... 37

Figure 9-13. Adding Buttons and 7-segment Displays to the Lightweight HPS-to-FPGA Bridge ......................... 38

Figure 9-14. Generate Qsys System ..................................................................................................................... 38

Figure 9-15. Qsys Component Instantiation ........................................................................................................ 40

Figure 9-16. Final Top-level Entity........................................................................................................................ 41

Figure 9-17. Correct HPS DDR3 Pin Assignment TCL Script Selection.................................................................. 42