www.ti.com

Usage Notes and Known Design Exceptions to Functional Specifications

7

SPRZ412G–December 2013–Revised July 2016

Submit Documentation Feedback Copyright © 2013–2016, Texas Instruments Incorporated

TMS320F2837xD Dual-Core Delfino™ Microcontrollers

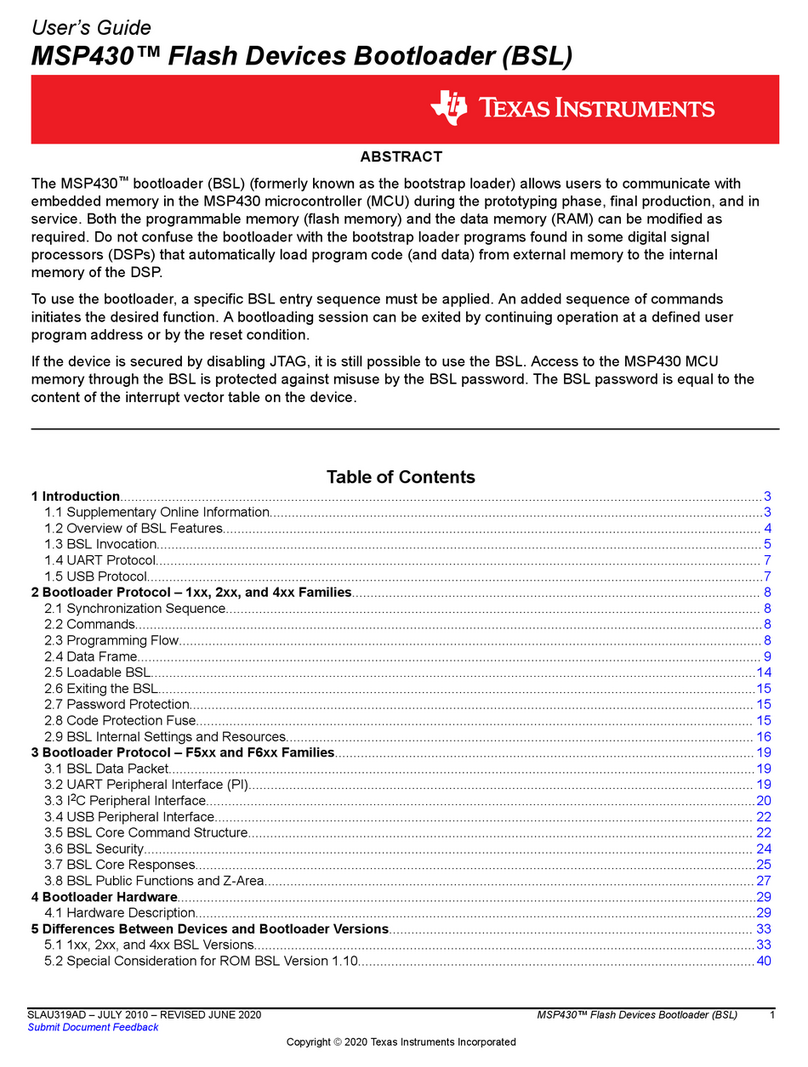

4.2 Known Design Exceptions to Functional Specifications

Table 3. Table of Contents for Advisories

Title ...................................................................................................................................... Page

Advisory —Analog Trim of Some TMX Devices ..................................................................................... 9

Advisory —ADC: ADC Post-Processing Block Limit Compare................................................................... 10

Advisory —ADC: ADC Offset Trim in Different Modes ............................................................................ 10

Advisory —ADC: Random Conversion Errors...................................................................................... 10

Advisory —ADC: ADC PPB Event Trigger (ADCxEVT) to ePWM Digital Compare Submodule ............................ 11

Advisory —ADC: 12-Bit Switch Resistance ........................................................................................ 11

Advisory —ADC: 12-Bit Input Capacitance When Switching Channel Groups ................................................ 11

Advisory —ADC: Functionality of VREFLO Pins....................................................................................... 12

Advisory —ADC: Sensitivity to ESD Events ....................................................................................... 12

Advisory —ADC: ADC Input Multiplexer Connection at Beginning of Acquisition Window................................... 12

Advisory —ADC: ADC Sparkle Codes............................................................................................... 13

Advisory —ADC: ADC Linearity Performance...................................................................................... 13

Advisory —XRS may Toggle During Power Up .................................................................................... 14

Advisory —USB: USB DMA Event Triggers are not Supported.................................................................. 14

Advisory —VREG: VREG Will be Enabled During Power Up Irrespective of VREGENZ .................................... 14

Advisory —Flash: A Single-Bit ECC Error May Cause Endless Calls to Single-Bit-Error ISR ............................... 14

Advisory —ePIE: Spurious VCU Interrupt (ePIE 12.6) Can Occur When First Enabled...................................... 15

Advisory —eQEP: Position Counter Incorrectly Reset on Direction Change During Index .................................. 15

Advisory —PLL: May Not Lock on the First Lock Attempt........................................................................ 16

Advisory —SDFM: Data Filter Output Does Not Saturate at Maximum Value With Sinc3 and OSR = 256................ 17

Advisory —SDFM: Spurious Data Acknowledge Event When Data Filter is Configured and Enabled for the First Time 17

Advisory —SDFM: Spurious Data Acknowledge Event When Data Filter is Synchronized Using PWM FILRES Signal 17

Advisory —SDFM: Comparator Filter Module may Generate Spurious Over-Value and Under-Value Conditions ....... 18

Advisory —SDFM: Dynamically Changing Threshold Settings (LLT, HLT), Filter Type, or COSR Settings Will Trigger

Spurious Comparator Events................................................................................................. 18

Advisory —SDFM: Dynamically Changing Data Filter Settings (Such as Filter Type or DOSR) Will Trigger Spurious

Data Acknowledge Events.................................................................................................... 18

Advisory —FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU 2p Operation............................. 19

Advisory —FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32 Instructions ............................... 20

Advisory —Memory: Prefetching Beyond Valid Memory ......................................................................... 22

Advisory —CMPSS: COMPxLATCH May Not Clear Properly Under Certain Conditions .................................... 23

Advisory —CMPSS: Ramp Generator May Not Start Under Certain Conditions .............................................. 23

Advisory —CMPSS: CMPIN4N, CMPIN4P, CMPIN5N, and CMPIN5P Not Available........................................ 23

Advisory —Boot ROM: Device Will Hang During Boot if X1 Clock Source is not Present ................................... 24

Advisory —HRPWM: HRCNFG Register Reads and Bit-Wise Writes .......................................................... 24

Advisory —SYSBIOS in ROM References Different Flash Sector (Changed From Sector A to Sector B) ................ 24

Advisory —McBSP: McBSP Transmit in SPI Slave Mode........................................................................ 25

Advisory —Crystal: Maximum Equivalent Series Resistance (ESR) Values are Reduced................................... 25

Advisory —GPIO: GPIO0–GPIO7, GPIO46, GPIO47 Shunt to VSS Due to Fast Transients at High Temperature........ 26

Advisory —Flash: Reset of CPU2 While it has Pump Ownership Can Cause Erroneous Flash Reads From CPU1..... 27