ISD1700 SERIES

Publication Release Date: February 7, 2006

- 5 - Revision 1.2

1 GENERAL DESCRIPTION

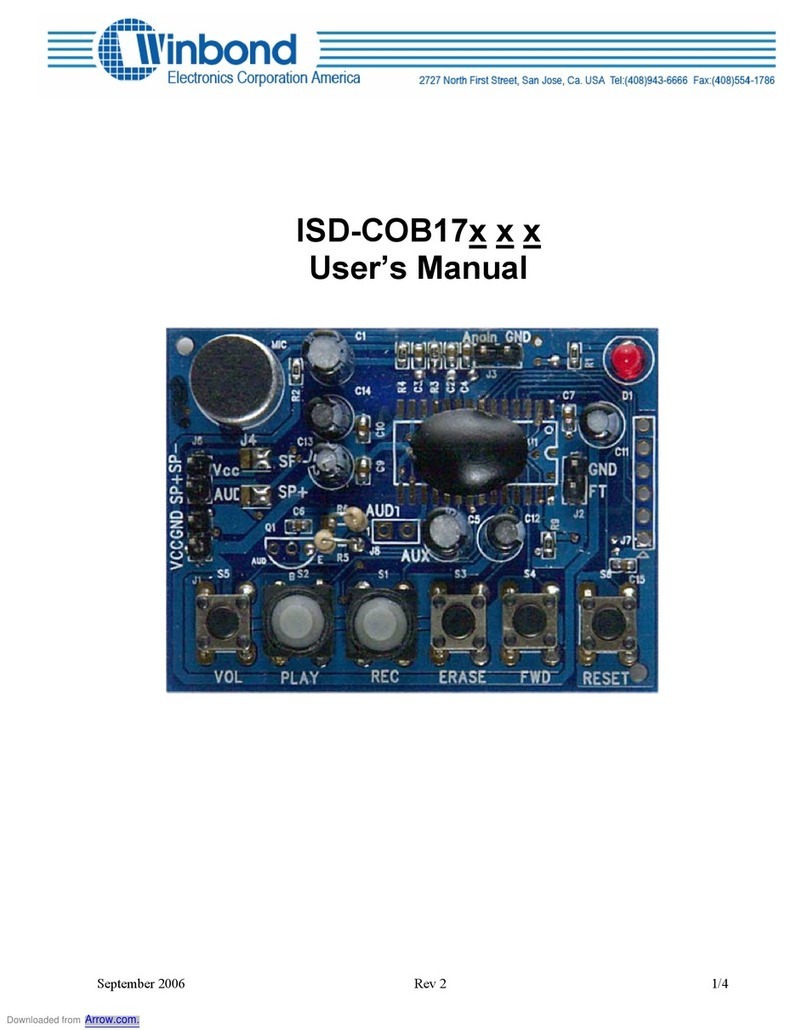

The Winbond®ISD1700 ChipCorder®Series is a high quality, fully integrated, single-chip multi-

message voice record and playback device ideally suited to a variety of electronic systems. The

message duration is user selectable in ranges from 26 seconds to 120 seconds, depending on the

specific device. The sampling frequency of each device can also be adjusted from 4 kHz to 12 kHz

with an external resistor, giving the user greater flexibility in duration versus recording quality for each

application. Operating voltage spans a range from 2.4 V to 5.5 V to ensure that the ISD1700 devices

are optimized for a wide range of battery or line-powered applications.

The ISD1700 is designed for operation in either standalone or microcontroller (SPI) mode. The device

incorporates a proprietary message management system that allows the chip to self-manage address

locations for multiple messages. This unique feature provides sophisticated messaging flexibility in a

simple push-button environment. The devices include an on-chip oscillator (with external resistor

control), microphone preamplifier with Automatic Gain Control (AGC), an auxiliary analog input, anti-

aliasing filter, Multi-Level Storage (MLS) array, smoothing filter, volume control, Pulse Width

Modulation (PWM) Class D speaker driver, and current output.

The ISD1700 devices also support an optional “vAlert” (voiceAlert) feature that can be used as a new

message indicator. With vAlert, the IC strobes an external LED to indicate that a new message is

present. Four special sound effect locations are reserved for audio confirmation of commands, such as

“Start Record”, “Stop Record,” and “Erase.”

Recordings are stored in on-chip Flash memory cells, providing zero-power message storage. This

unique single-chip solution is made possible through Winbond’s patented Multi-Level Storage (MLS)

technology. Audio data are stored directly in solid-state memory without digital compression, providing

superior quality voice and music reproduction.

Voice signals can be fed into the chip through two independent paths: a differential microphone input

and a single-ended analog input. For outputs, the ISD1700 provides a Pulse Width Modulation (PWM)

Class D speaker driver and a separate analog output simultaneously. The PWM can directly drive a

standard 8Ωspeaker or typical buzzer, while the separate analog output can be configured as a

single-ended current or voltage output to drive an external amplifier.

The ISD1700 devices automatically enter into power down mode for power conservation when an

operation is completed.

In the SPI mode, the user has full control via the serial interface in operating the device. This includes

random access to any location inside the memory array by specifying the start address and end

address of operations. SPI mode also allows access to the Analog Path Configuration (APC) register.

This register allows flexible configuration of audio paths, inputs, outputs and mixing. The APC default

configuration for standalone mode can also be modified by storing the APC to a non-volatile register

(NVCFG) that is loaded at initialization. Utilizing the capabilities of ISD1700 Series, designers have

the control and flexibility to implement high-end products.

Notice: The specifications are subject to change without notice. Please contact Winbond Sales Offices or

Representatives to verify current or future specifications. Also refer to the website for any related application notes.