W78C438C

- 6-

FUNCTIONAL DESCRIPTION

The W78C438C is a functional extension of the W78C58 microcontroller. It contains a 256 ×8 RAM,

64 KB program/1 MB data memory address or memory-mapped chip select logic, two 8-bit address

ports, one 8-bit data port, five general I/O ports, four external interrupts, three timers/counters, and

one serial port.

Dedicated Data and Address Port

The W78C438C provides four general-purpose I/O ports for W78C32 applications; the address and

data bus are separated from Port 0 and Port 2 so that these ports can be used as general-purpose I/O

ports. In this product, DP4 is the data bus for external ROM and RAM, AP5<7:0> are the low byte

address, AP6<7:0> are the high byte address,

enables the external ROM to DP4, and P3.6

(

) and P3.7 (

) are the write/read control signals for the external RAM. The external latch for

multiplexing the low byte address is no longer needed in this product. The W78C438C uses AP5 and

AP6 to support 64 KB external program memory and 64 KB external data memory, just as a standard

W78C32 does.

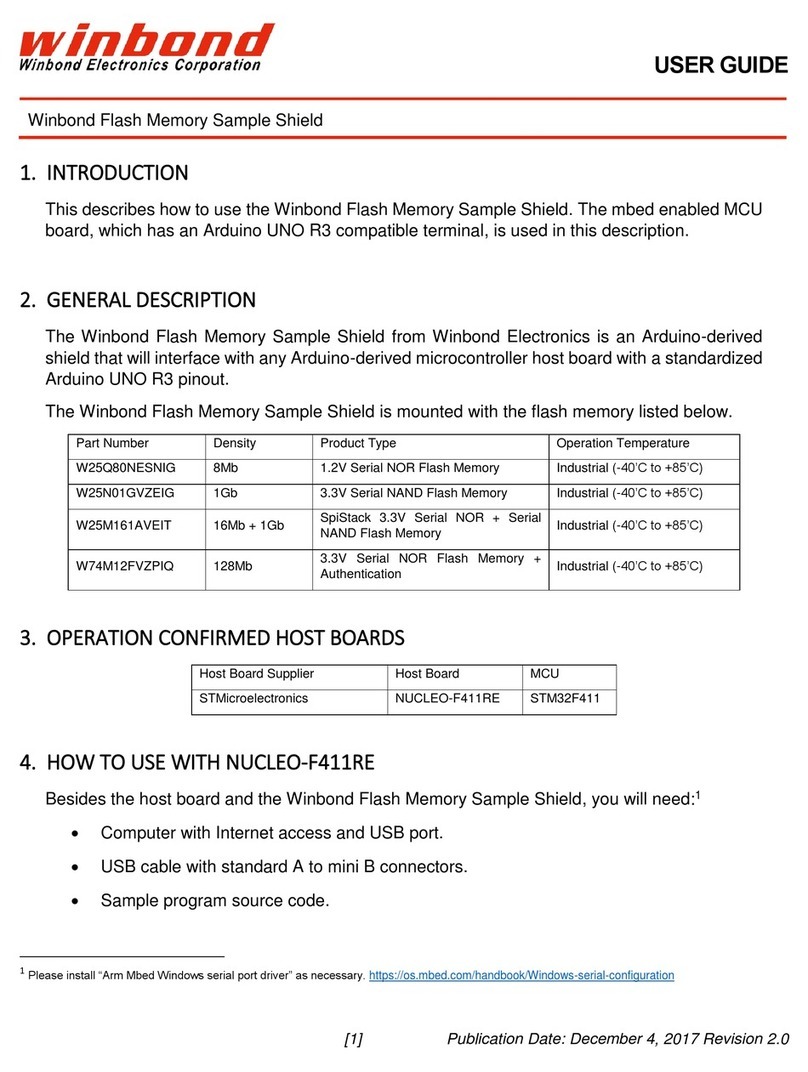

The W78C438C provides four pins, AP7.3−AP7.0 (CS3−CS0), to support either 64 KB program/1 MB

data memory space or memory-mapped chip select logic. Bit 7 of the EPMA (Extended Program

Memory Address) register, which is described in Table 1 below, determines the functions of these

pins.

When this bit is "0" (the default value), AP7<3:0> support external program/data memory addresses

up to 64 KB/1 MB for applications which need additional external memory to store large amounts of

data.

Although there is 1M bytes memory space, instructions stored here can not be run at full range of this

area except the first 64 Kbytes. It is owing to the fact that during the instruction fetch cycle, AP7<3:0>

always output 0s to address lines A19−A16. This limits the program code to store at address 0−

0FFFFH (64K). The rest of the area (10000H−FFFFFH) can be treated as ROM data storage which

can be read by "MOVC A, @A+DPTR" instruction.

When "MOVC A, @A+DPTR" is executed to read the external ROM data or "MOVX dest, src" is

executed to access the external RAM data, AP7<3:0> output address <19:16> from bits <3:0> of the

EPMA (Extended Program Memory Address) register. At other times, AP7<3:0> always output 0H to

ensure the instruction fetch is within the 64K program memory address. Different banks can be

selected by modifying the content of the EPMA register before the execution of "MOVC A,

@A+DPTR" or "MOVX dest, src."

[Example]. Access the external ROM/RAM data from external memory space.

CLR A; Clear Accumulator.

MOV DPTR, #0H ; Clear DPTR.

MOV 0A2H, #02 ; Initialize EPMA(0A2H). EPMA.7 = 0: extended memory space

; EPMA.<3:0> = 0010B, the address range: 20000−2FFFFH.

MOVC A, @A+DPTR ; Read the external ROM data from location 20000H.

MOVX A, @DPTR ; Read the external RAM data from location 20000H.

CLR A

MOV 0A2H, #03H ; EPMA.<3:0> = 0011B, the address range: 30000H−3FFFFH.

MOVC A, @A+DPTR ; Read the external ROM data from location 30000H.

MOVX @DPTR, A ; Write the contents of Accumulator to external RAM data.

; location 30000H.