AMD -K6-2/450 - MHz Processor Installation and operating instructions

Other AMD Computer Hardware manuals

AMD

AMD Geode SC2200 Product guide

AMD

AMD NVMe/SATA RAID User manual

AMD

AMD NOVELL 64 User manual

AMD

AMD ATHLON 8 User manual

AMD

AMD Athlon XP 10 User manual

AMD

AMD LE-366 User's User manual

AMD

AMD Geode SC3200 Product guide

AMD

AMD Athlon User manual

AMD

AMD 3800 - Processor - 1 x Athlon 64 Instruction sheet

AMD

AMD 780E Product manual

AMD

AMD Sempron 10 User manual

AMD

AMD MulTView ALL-IN-WONDER 9700 PRO User manual

AMD

AMD Geode NX 1250 User manual

AMD

AMD ADA3800DAA5BV Operational manual

AMD

AMD AMD 785G User manual

AMD

AMD Athlon Processor x86 User manual

AMD

AMD SP5100 Product guide

AMD

AMD Richland User manual

AMD

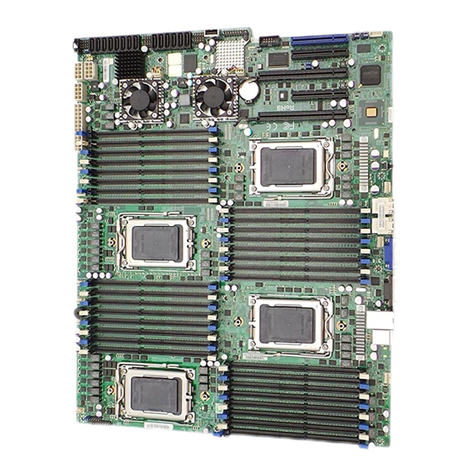

AMD OPTERON 30925 User manual

AMD

AMD 790GX User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual

Galaxy

Galaxy GHDX2-2430S-24F4D Installation and hardware reference manual

Intel

Intel AXXRMFBU4 Quick installation user's guide

Kontron

Kontron DIMM-PC/MD product manual

ST

ST X-NUCLEO-SAFEA1B How to use

STEINWAY LYNGDORF

STEINWAY LYNGDORF SP-1 installation manual

Advantech

Advantech ASMB-935 Series user manual