AD9739

Rev. A | Page 2 of 56

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

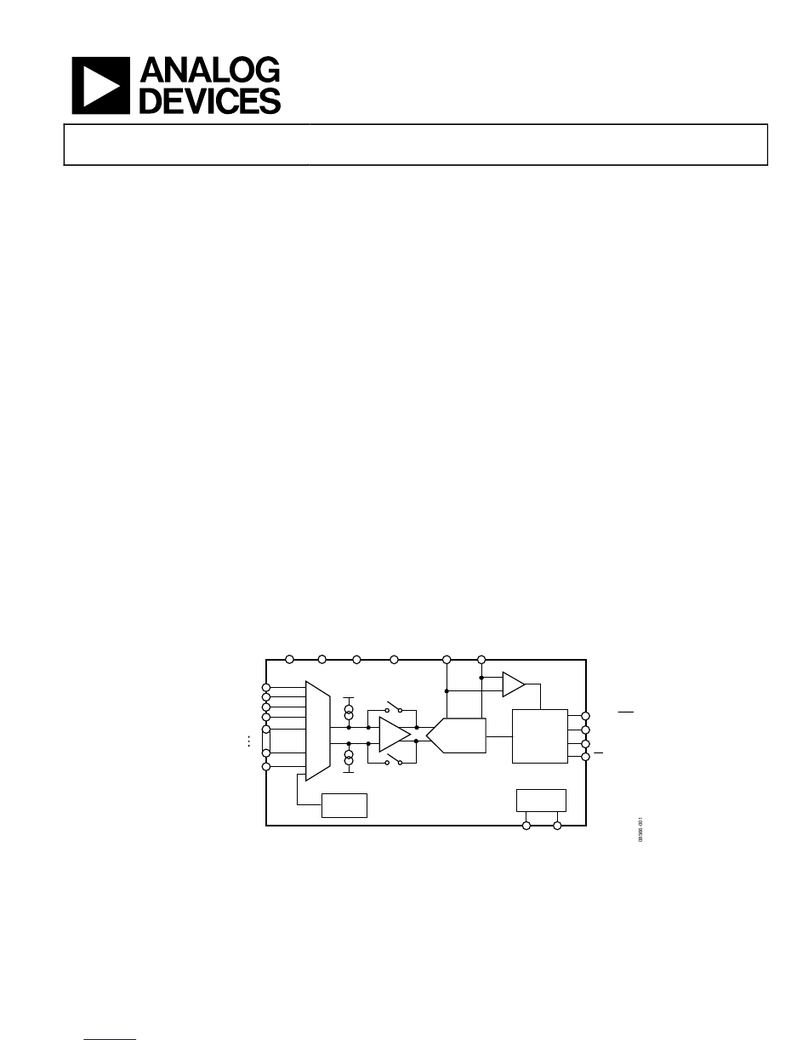

General Description ......................................................................... 1

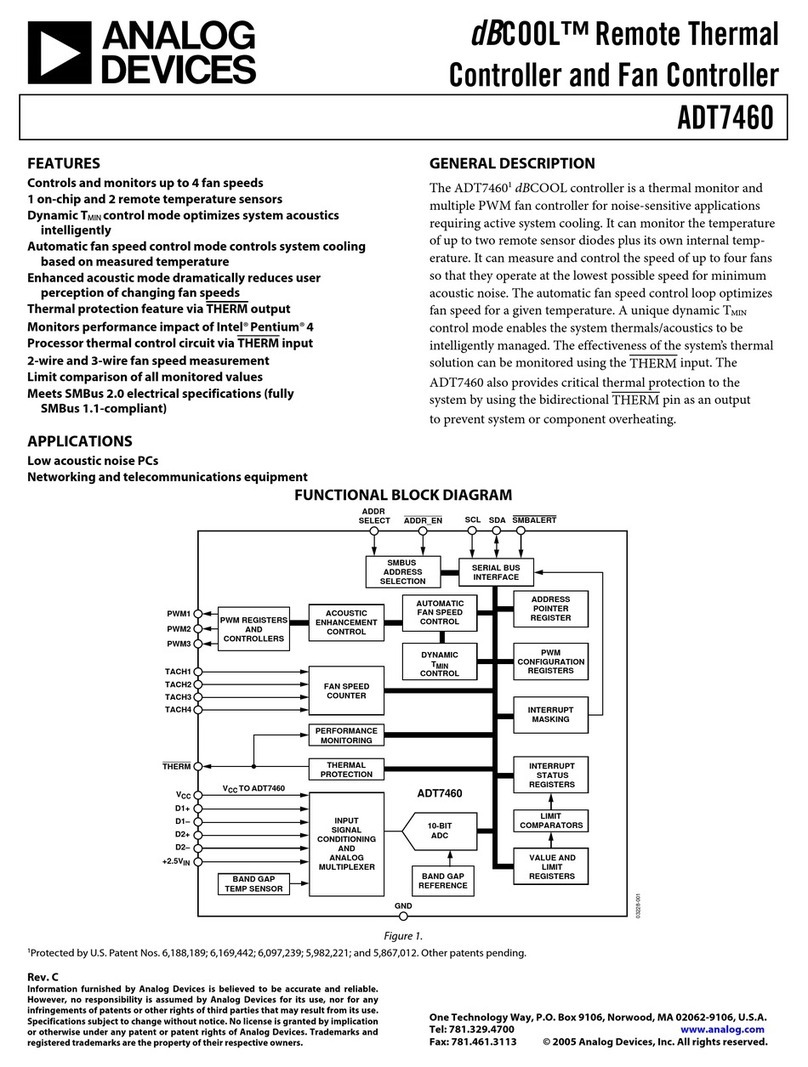

Functional Block Diagram .............................................................. 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

DC Specifications ......................................................................... 3

Digital Specifications ................................................................... 4

AC Specifications.......................................................................... 5

Absolute Maximum Ratings............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution.................................................................................. 7

Pin Configurations and Function Descriptions ........................... 8

Typical Performance Characteristics ........................................... 11

Static Linearity ............................................................................ 11

Dynamic Performance Normal Mode, 20 mA Full Scale

(Unless Otherwise Noted)......................................................... 13

Dynamic Performance Mix Mode, 20 mA Full Scale............ 17

DOCSIS Performance................................................................ 19

Terminology .................................................................................... 24

Theory of Operation ...................................................................... 25

Serial Peripheral Interface ......................................................... 25

General Operation of the Serial Interface ............................... 25

Instruction Mode (8-Bit Instruction) ...................................... 25

Serial Interface Port Pin Descriptions ..................................... 25

SCLK—Serial Clock............................................................... 25

CS—Chip Select...................................................................... 25

SDIO—Serial Data I/O.......................................................... 25

SDO—Serial Data Out........................................................... 25

MSB/LSB Transfers..................................................................... 26

Serial Port Configuration .......................................................... 26

SPI Register Map ............................................................................ 27

SPI Registers................................................................................ 28

Applications Information .............................................................. 37

Analog Modes of Operation ..................................................... 37

LVDS Data Port Interface.......................................................... 37

Clocking the AD9739 ................................................................ 39

Applying Data to the AD9739 .................................................. 40

Mu Delay Controller.................................................................. 41

Mu Control Operation............................................................... 41

Search Mode ........................................................................... 41

Track Mode ............................................................................. 42

Mu Delay and Phase Readback ............................................ 42

Operating the Mu Controller Manually.............................. 42

Calculating Mu Delay Line Step Size................................... 42

Synchronization Controller ...................................................... 43

Operation in Master Mode ................................................... 44

Operation in Slave Mode ...................................................... 45

Data Receiver Operation in Auto Mode ................................. 45

Data Receiver Operation in Manual Mode............................. 46

Calculating the DCI Delay Line Step Size .......................... 46

Maximum Allowable Data Timing Skew/Jitter ...................... 46

Optimizing the Clock Common-Mode Voltage .................... 47

Analog Control Registers .......................................................... 47

Mirror Roll-Off Frequency Control......................................... 47

Voltage Reference ....................................................................... 47

Analog Outputs .......................................................................... 48

Interrupt Requests...................................................................... 49

Recommended Start-Up Sequence .......................................... 50

Outline Dimensions....................................................................... 53

Ordering Guide .......................................................................... 53

REVISION HISTORY

7/11—Rev 0 to Rev A

Changes to Table 2, DAC CLOCK INPUT (DACCLK_P,

DACCLK_N), Added DAC Clock Rate......................................... 4

Changes to Table 3, Added Dynamic Performance

Parameters ......................................................................................... 5

Change to Ordering Guide............................................................ 53

1/09—Revision 0: Initial Version