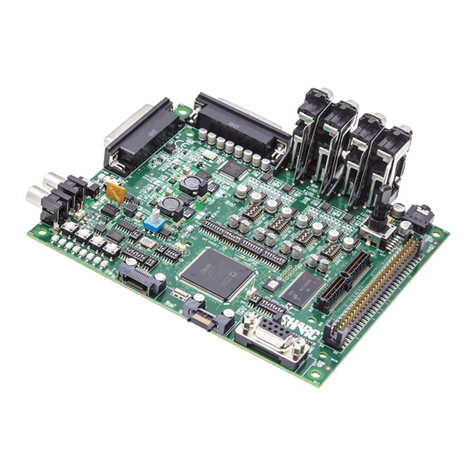

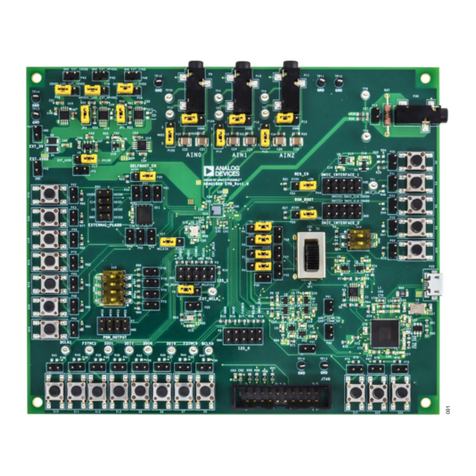

Jumpers ....................................................................................................................................................... 3–13

S/PDIF Loopback ( JP2 )......................................................................................................................... 3–13

CAN INH ( JP3 ) .................................................................................................................................... 3–13

Regulator Disable ( JP4 ) ......................................................................................................................... 3–14

Current Measurement ( P17, P18, P20, P21 and P24 ) .................................................................. 3–14

HADC ( P25 ).......................................................................................................................................... 3–14

LEDs ........................................................................................................................................................... 3–14

Fault ( LED1 ) ........................................................................................................................................... 3–15

USB to UART Activity ( LED2-3 )........................................................................................................... 3–15

BCM89810 Status ( LED4-6 ).................................................................................................................. 3–15

A2B Interrupt ( LED8 ) ............................................................................................................................. 3–16

Power ( LED9 ) ......................................................................................................................................... 3–16

GPIO ( LED10-17 )................................................................................................................................. 3–16

Reset ( LED22 )......................................................................................................................................... 3–16

DP83865 Status ( LED23-26 )................................................................................................................. 3–16

Connectors .................................................................................................................................................. 3–17

S/PDIF Optical Tx ( J1 ) ......................................................................................................................... 3–17

Clock ( J2 ) .............................................................................................................................................. 3–18

Audio Input/Output ( J3 ) ....................................................................................................................... 3–18

Ethernet 10/100/1000 ( J4 ) .................................................................................................................... 3–18

CAN ( J5 and J6 ) ................................................................................................................................ 3–18

Ethernet 10/100 ( J7 ) ............................................................................................................................. 3–18

Link Port/JTAG ( J8 and J9 ) ............................................................................................................... 3–18

S/PDIF Optical Rx ( J10 ) ....................................................................................................................... 3–19

Audio Output ( J11 ) ............................................................................................................................... 3–19

S/PDIF Digital ( J12 ) ............................................................................................................................. 3–19

MLB ( J13 )............................................................................................................................................. 3–19

Headphone ( J14 ) ................................................................................................................................... 3–19

HADC ( J15-J17 and J19 ) ................................................................................................................ 3–20

ADSP-SC573 EZ-KIT ® Manual v

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.