Safety Instr ctions

● When working with the ECS-PMC/FPGA follow the instructions below and read the manual carefully to protect yourself

from injury and the ECS-PMC/FPGA from damage.

● The device is a built-in component. It is essential to ensure that the device is mounted in a way that cannot lead to

endangering or injury of persons or damage to objects.

● The device has to be securely installed in the control cabinet before commissioning.

● Protect the ECS-PMC/FPGA from dust, moisture and steam.

● Protect the ECS-PMC/FPGA from shocks and vibrations.

● The ECS-PMC/FPGA may become warm during normal use. Always allow adequate ventilation around the ECS-

PMC/FPGA and use care when handling.

● Do not operate the ECS-PMC/FPGA adjacent to heat sources and do not expose it to unnecessary thermal radiation.

Ensure an ambient temperature as specified in the technical data.

● Do not use damaged or defective cables to connect the ECS-PMC/FPGA.

● In case of damages to the device, which might affect safety, appropriate and immediate measures must be taken, that

exclude an endangerment of persons and domestic animals and property.

● Current circuits which are connected to the device have to be sufficiently protected against hazardous voltage (SELV

according to EN 60950-1).

● The ECS-PMC/FPGA may only be driven by power supply current circuits, that are contact protected.

A power supply, that provides a safety extra-low voltage (SELV) according to EN 60950-1, complies with this

conditions.

Danger!

Hazardous Voltage - Risk of electric shock due to unintentional contact with uninsulated live parts with high

voltages inside of the system into which the ECS-PMC/FPGA is to be integrated. Disconnect all hazardous

voltages (mains voltage) before opening the system.

Attention !

Electrostatic discharges may ca se damage to electronic components.

To avoid this, please perform the steps described on page 16 before you touch the ECS-PMC/FPGA, in

order to discharge the static electricity from your body.

Q alified Personal

This documentation is directed exclusively towards personal qualified in control and automation engineering.

The installation and commissioning of the product may only be carried out by qualified personal, which is authorized to

put devices, systems and electric circuits into operation according to the applicable national standards of safety

engineering.

Conformity

The ECS-PMC/FPGA is a sub-assembly intended for incorporation into an apparatus by a manufacturer and NOT by the

end user. The manufacturer of the final system must decide, whether additional EMC or EMI protection requirements are

necessary.

Data Safety

This device is equipped with an Ethernet or other interface which is suitable to establish a connection to data networks.

Depending on the software used on the device, these interfaces may allow attackers to compromise normal function, get

illegal access or cause damage.

esd does not take responsibility for any damage caused by the device if operated at any networks. It is the responsibility

of the device's user to take care that necessary safety precautions for the device's network interface are in place.

Intended Use

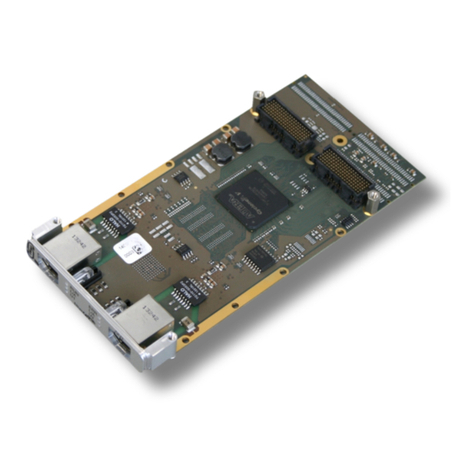

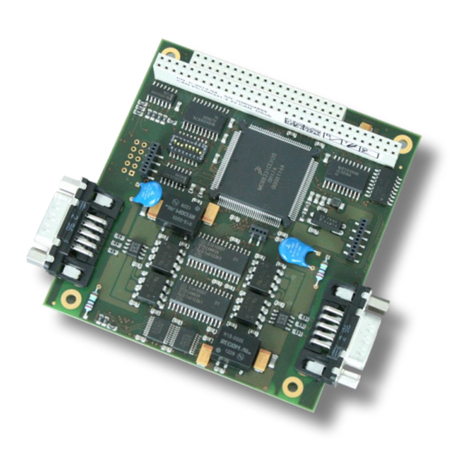

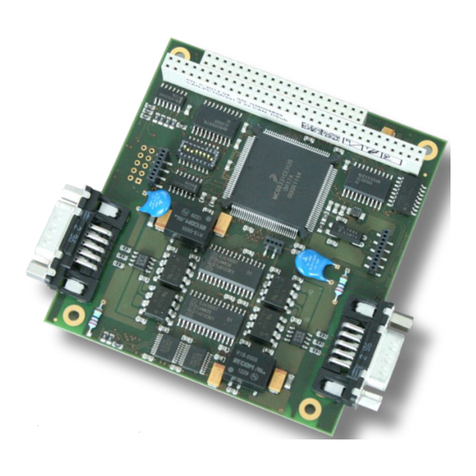

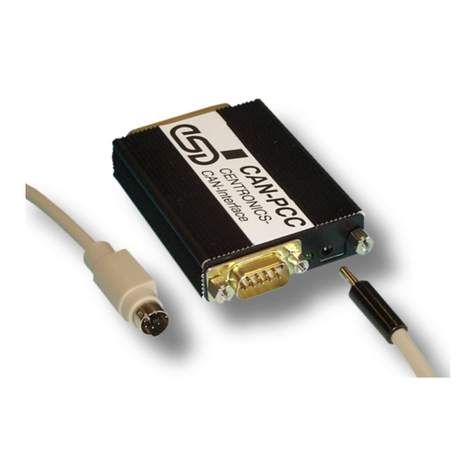

The intended use of the ECS-PMC/FPGA is the operation as PMC EtherCAT® Slave Interface.

The guarantee given by esd does not cover damages which result from improper use, usage not in accordance with

regulations or disregard of safety instructions and warnings.

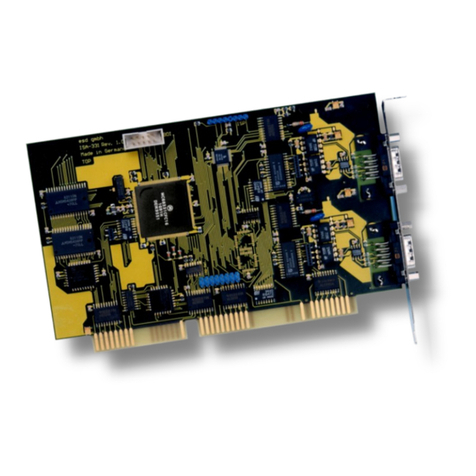

● The ECS-PMC/FPGA is intended for installation on a base board according to IEEE 1386.1-2001 (PMC) .

● The operation of the ECS-PMC/FPGA in hazardous areas, or areas exposed to potentially explosive materials is not

permitted.

● The operation of the ECS-PMC/FPGA for medical purposes is prohibited.

Service Note

The ECS-PMC/FPGA does not contain any parts that require maintenance by the user. The ECS-PMC/FPGA does not

require any manual configuration of the hardware.

Disposal

Devices which have become defective in the long run have to be disposed in an appropriate way or have to be returned

to the manufacturer for proper disposal. Please, make a contribution to environmental protection.

Page 4 of 26 Hardware Manual • Doc. No. E.1104.21 / Rev. 1.1 ECS-PMC/FPGA