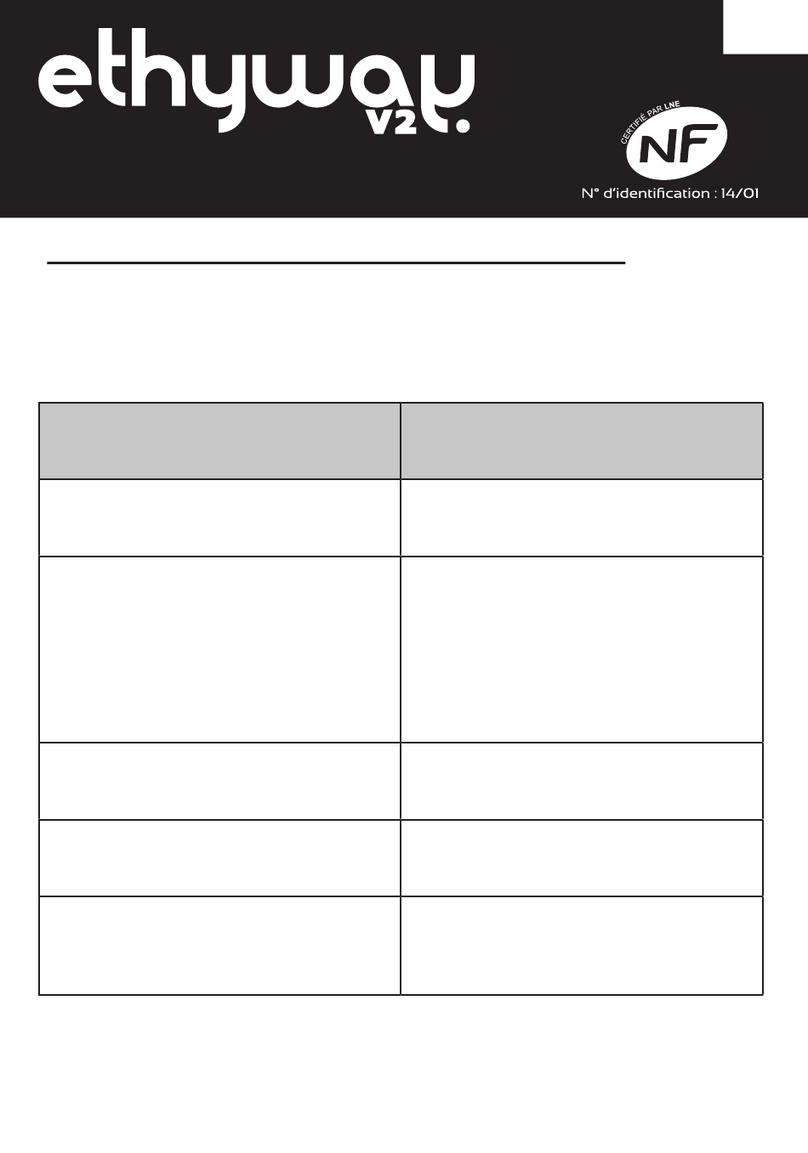

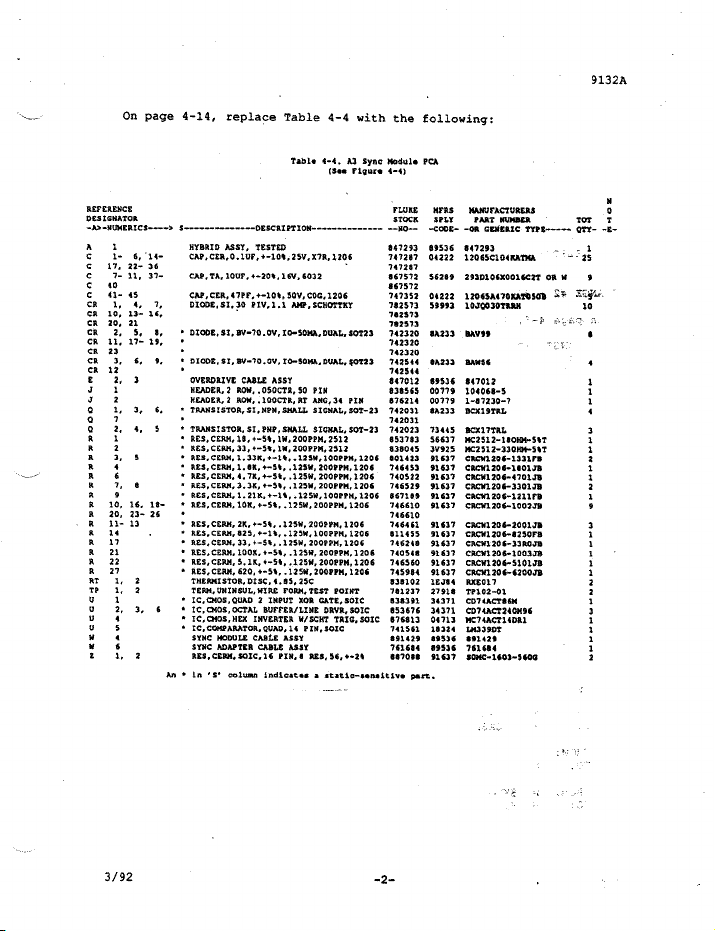

On page 4-14,

Table 4-4. Al Sync Module

(Sas Flgure 4-4)

FLUKE

STOCK

weRQum

847293

747287

147287

867572

867572

747352

782573

782873

782573

742320

742320

742320

742544

42548

847012

838565

876214

742031

742031

742023

853783

838045

201423

746453

740522

746529

#67109

746610

745610

746461

$11455

746248

740548

746560

745984

838102

181237

833391

853676

876813

T4156

£91429

761684

ss7088

MFRS

seLy

“CODE

89536

04222

$6289

04222

53993

A233

8A233

89536

00779

00779

A233

T3445

56637

3vezs

91637

91637

91637

91637

91637

91637

1637

91637

91627

91637

91632

91637

REFERENCE

DESIGHATOR

UM 127"

A1HYBRID ASSY, TESTED

<1-6, '14= CAP, CER, 0.1UF, +~108,25V,X7R, 1206

<17, 22-36 *

Cc 7-13, 37- CAP, TA, 10UF, +~20%, 16V, 6032

< 40

C41-45 CAP, CER, 47BF, +=10%, 50V, C0G, 1206

CRY, 4, 7, DIODE, S$I,30 £1IV,1.1 AMP, SCHOTTKY

CR 10, 13- 16, :

CR 20, 21

CR 2, 58, *DIODE, $I, BV=70.0V, 10=50MA, DUAL, $0723

CR 11, 17- 13, *

CR 23 =

CR 3, 69, *DICQDE, $I, BV=~70.0V, IO=$0MA, DUAL, §0T23

CR 12 *

t2, 3QVERDRIVE CABLE ASSY

J1HEADER, 2ROW, ,050CTR, 50 PIN

J2HEADER, 2ROW, .100CTR, RT ANG, 34 PIN

Qe i, 3, 6, *TRANSISTOR, SI, NPN, SMALL SIGNAL, S0T~23

Q7*

Q2, 45*TRANSISTOR, ST, PNP, SMALL SIGNAL, $OT-23

R1*RES, CERM, 18, +-5%, IW, 200PPH, 2512

R2*RES,CERM, 31, +~5%, IW, 200PPN, 2512

R3, 8©RES, CERM, 133K, +-1%, .125W, 1002PN, 1206

R4*RES, CERM, 1.8K, +~5%, (125W, 2000PH, 1206

Ré«RES,CERM, 4, 7K, +~5%, .125W, 200PPN, 1206

R7, *RES,CERM, 3.3K, +~5%, (125W, 200PPM, 1206

R9*RES, CERM, 1,21K, +-1%,.125W,100PPN, 1206

R16, 16, 18- * RES,CERM, 10X, +-5¢, 125W, 200PPN, 1206

R20, 23- 26 *

R11-13 *RES, CERM, 2K, 4-54, ,125W, 200PPN, 1206

R24 .*RES,CERM, 825, +-1%, .125W, 100PPH, 1206

R17 *RES, CERM, 33, +~5%, ,125W, 200PPM, 1206

R21 *RES, CERM, 100K, +~5%, ,125, 2008PM, 1206

R22 *RES, CERM, 5.1K, +-54, .125W, 200PPN, 1206

R27 *RES,CERM, 620, +~5%, .125W, 200PPM, 1206

RT i, 2THERMISTOR, DISC, 4.98, 25¢C

T® i, 2TERM, UNINSUL, WIRE FORM, TEST POINT

u1*1C,CMOS,QUAD 2INPUT XOR GATE, SOIC

u2, 3€+1C, CMOS, 0CTAL BUFFER/LINE DRVR, SOIC

u4*IC, CMOS, HEX INVERTER W/SCHT TRIG, SOIC

u5¢IC, COMPARATOR, QUAD, 14 PIN,S0IC

Ww 4SYNC MODULE CABLE ASSY

»6SYNC ADAPTER CABLE ASSY

z1, 2RES, CERM, SOIC,16 PIN, 8RRS, 36, 42%

An *in ‘S* column indicates astatic-sensitive part.

3/92 ww

replace Table 4-4 with the following:

9132A

N

MANUFACTURERS 0

PART NUMBER :TOT T

-OR GENERIC TYPEw-wen QTY~ ~E-

947293 1

12065C104RATMA a5

293D106X0016C2T OR W9

17065A070KATOSOD SF Fags

10

100030 TARE

Jeb

BAVSS

BAWSS

847012

104068-3

1-87230-7

BCXISTRL

BCX1TTRL

MC2512-180HM-SAT

MC2512-330KM-54T

CRON1206~1331F8

CRCW1206+180108

CRCW1206~4701J8

CRCWL206-330108

CRCW1206-1211FD

CRECW1206-100209

CRCW1206~200178

CRCW1206-8250FB

CRCWY206-33R058

CRCW1206+-100308

CRCW1206~510108

CRCW1206-$20008

CDTAACT240M9€

761684

S0MC~1603~560G

-

a

fT

EE

LL

an