Circuit Description Section

4

Figures 2, 3 and

4

show the circuit details of the Y ampli-

fier, timebase and power supplies respectively. Fig.

5

shows their inter-connection but for clarity some details

of this inter-connection are included in the detailed

diagrams also. For convenience, the circuit reference of

any component can be used to determine its location in

the instrument.

1

-

99 Frame or interconnection

100

-

199 CHI Pre-amplifiers,trigger amplifier

beam switch, beam switch bistable.

200

-

299 CH2 Pre-amplifiers, trigger amplifier.

300

-

399 Delay line drive, equaliser, Y O/P

amplifier, bistable drive and X/Y

amplifier.

Trigger Timebase, delay and X O/P

600

-

699

700

-

799) Power Supply

800

-

899 Front Panel Control Board

900

-

999 E.H.T. Supply.

e.g. R309 is part of the Delay Line Drive.

The circuit diagrams are generally arranged for each

printed board assembly or group of boards. These

diagrams include some of the switches, potentiometers

etc., closely associated with the circuit although these

components may be mounted on the frame.

Consequently not all such components appear on the

interconnection diagram Fig.

5

and where it makes the

circuits easier to follow, some components appear on

more than one circuit.

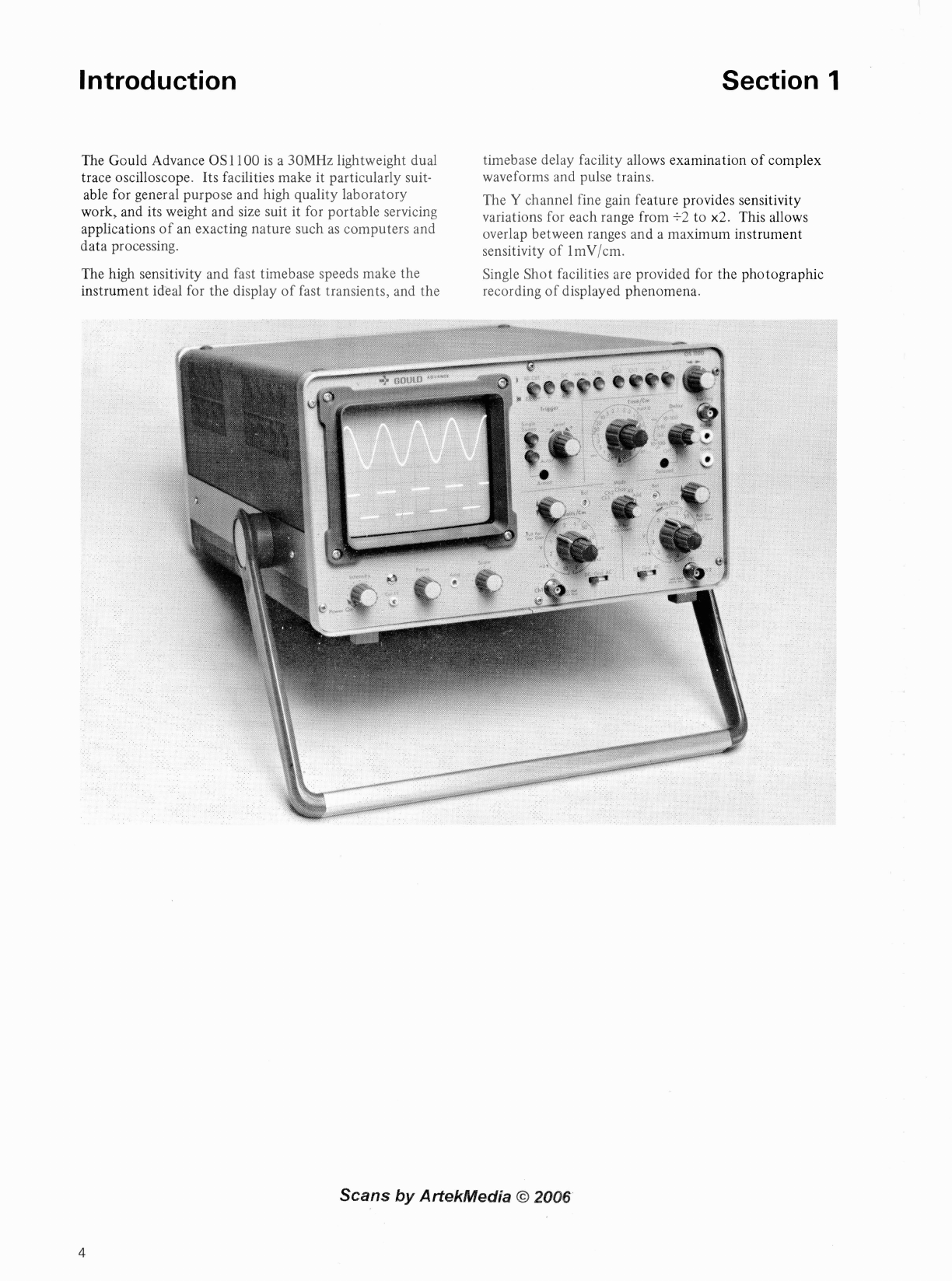

4.1

THE BLOCK DIAGRAM

The block diagram for the complete instrument is shown

in Fig.

1.

It is not intended to be a full working diagram

but gives details of the functional points of the circuit

and their inter-relation. The circuit can be readily

divided into three main sections which are:

Y deflection circuits, X deflection circuits (including

timebase delay and trigger circuits) and Power Supply

which includes Bright-up functions.

Y

CHANNELS

The switched attenuator,pre-amplifier and trigger

amplifier are identical for the two Y channels except

that CH1 provides pick-off and amplification for the X/Y

signal and CH2 provides invert facilities. The selection

of the decade steps of the attenuator and 1.2.

5.

sequence of pre-amplifier gain switching are determined

by the sensitivity selected.

The use of the fine gain facility on either channel allows

a 2:1 increase or decrease in sensitivity.

The channel switch is a fast electronic switch with the

equivalent of a change-over action as shown. It selects

either the CH1 or the CH2 signal to be passed to the sub-

sequent stages and is controlled from a J-K flip-flop. The

state of the flip-flop and hence the channel selection is

determined by d.c.voltages applied to its preset and clear

inputs. In the chop mode, the J-K flip-flop is driven via

its clock input and a signal gate from a free running

monostable, switching the beam between CHI and CH2

signals as the X sweep progresses. In the alternate mode,

end of sweep pulses are fed from the timebase to the J-K

via the signal gate and reverse the beam switch at the end

of each timebase sweep, giving alternate CH1 and CH2

sweeps. In the ADD mode, both the CHI and CH2

switches are closed and the two signals are summed

algebraically. On CH1 or CH2,the appropriate switch is

closed, allowing only that signal to pass.

The signal from the selected channel is passed via a delay

line and amplifiers to the Y deflection plates of the c.r.t.

The delay allows examination of that point in the wave-

form which triggered the sweep since the deflecing signal

reaches the Y plates after the timebase sweep and bright-

up have been initiated.

THE TIMEBASE

The purpose of the timebase system is to generate a linear

ramp to deflect the spot in the X direction. The trigger

system initiates each sweep from the incoming or other

signals, normally to obtain a stationary display of a

repeated waveform.

The internal or external trigger signal as selected is

amplified by the trigger amplifier which is biased by the

required trigger level, and the resultant is amplified and

passed to drive the trigger circuit. If the timebase is

ready to commence a sweep, a transition of the trigger

circuit will set the timebase bistable which in turn initiates

the ramp. This signal is passed via the X amplifier to the

X

deflection plates of the c.r.t.

At the end of the sweep, the bistable is reset, returning

the ramp to the original level. During the period of sweep,

the trigger gate is prevented from passing trigger pulses to

the bistable and this inhibition is maintained by the hold-

off circuit until the ramp generator is fully recovered,

ready for the next sweep to commence on the next trigger

pulse, when the cycle is repeated.

In the delay mode the timebase bistable is triggered in the

same manner but the bistable output to the ramp

generator is inhibited for the period of the delay. To

allow time for the delay monostable to fully reset there

is an additional hold-off control from the delay circuit

into the trigger gate. In Single Sweep, the relevant

bistable normally inhibits the trigger pulses from reaching

the timebase bistable by biasing the hold-off circuit, and

hence closing the trigger gate. When the single sweep

bistable is armed the trigger gate is opened and the next

trigger pulse initiates a sweep. At the end of the sweep

the single sweep bistable is reset, preventing the timebase

from sweeping again until the manual ARM button is

pressed once more.

The trigger signal for the timebase, selected from either

internal, external, or line frequency sources, is passed

through the required processing filter selected by the

Scans

by

Arte