4 - 2

4-1-5 AF AMPLIFIER CIRCUIT

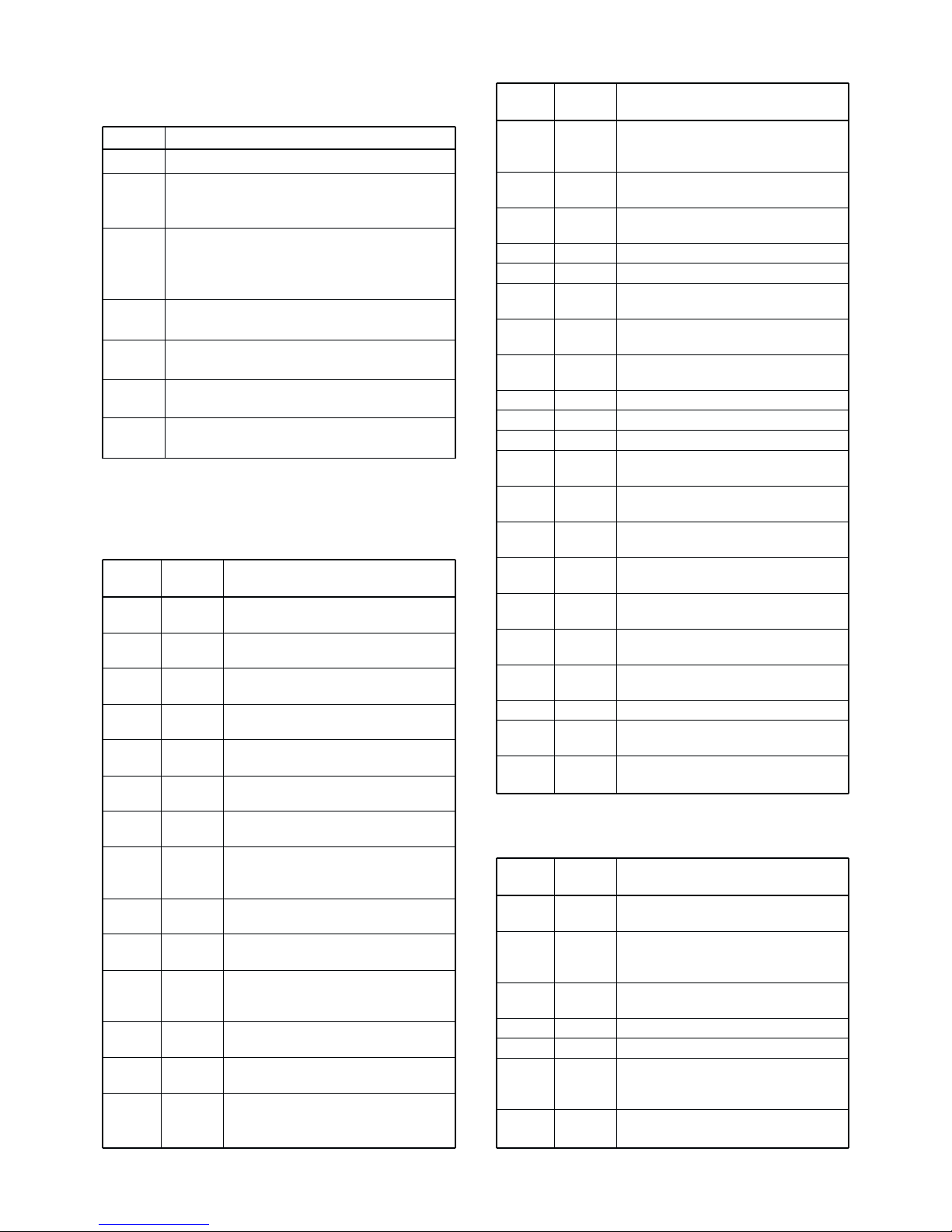

The AF amplifier circuit amplifies the demodulated AF sig-

nals to drive a speaker.

The AF signals from the FM IF IC (IC3, pin 9) are amplified

at the AF amplifier section of the compander IC (IC9, pins 5,

4) and are then applied to the high-pass filter circuit (IC10).

The high-pass filter characteristics are controlled by the

FSW signal from the I/O expander IC (IC23, pin 14). When

FSW signal is high, the cut-off frequency is shifted higher to

remove CTCSS or DTCS signals.

The filtered AF signals from the high-pass filter (IC10, pin 4)

are applied to the de-emphasis section of compander IC

(IC9, pin 3) with frequency characteristics of –6 dB/octave,

and are then passed through the low-pass filter, high-pass

filter, expander sections of compander IC (IC9). The output

signal from IC9 (pin 38) is applied to the electronic volume

controller (IC13, pin 1).

The output AF signals from the electronic volume controller

(IC13, pin 2) are applied to the AF power amplifier (IC5) to

drive the speaker.

4-1-6 RECEIVE MUTE CIRCUITS

• NOISE SQUELCH

A squelch circuit cuts out AF signals when no RF signals are

received. By detecting noise components in the AF signals,

the squelch circuit switches the AF mute switch.

Some noise components in the AF signals from the FM IF IC

(IC3, pin 9) are passed through the level controller (IC13,

pins 24, 23). The level controlled signals are applied to the

active filter section in the FM IF IC (IC3, pin 8). Noise com-

ponents about 10 kHz are amplified and output from pin 7.

The filtered signals are converted into the pulse-type signals

at the noise detector section and output from pin 13 (NOIS).

The NOIS signal from the FM IF IC is applied to the CPU

(IC14, pin 75). The CPU then analyzes the noise condition

and controls the AF mute signal via “AFMT”line (IC23, pin

13) to the AF regulator (Q23, Q24).

•CTCSS AND DTCS

The tone squelch circuit detects AF signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS or DTCS). When tone squelch is in

use, and a signal with a mismatched or no subaudible tone

is received, the tone squelch circuit mutes the AF signals

even when noise squelch is open.

A portion of the AF signals from the FM IF IC (IC3, pin 9)

passes through the low-pass filter (IC20b/a) to remove AF

(voice) signals and is applied to the CTCSS or DTCS

decoder inside of the CPU (IC14, pin 46) via the “RXDT”line

to control the AF mute switch via the I/O expander IC (IC23).

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

The microphone amplifier circuit amplifies audio signals

within +6 dB/octave pre-emphasis characteristics from the

microphone to a level needed for the modulation circuit.

The AF signals (MIC+) from the FRONT unit via J3 (pin 22)

are passed through the internal/extenal microphone switch

(IC19, pins 7, 1) and level controller (IC13, pins 9, 10) to the

microphone amplifier circuit.

The AF signals from the level controller (IC13) are applied to

the microphone amplifier section of compander IC (IC9, pin

12). The amplified signals are passed through the compres-

sor, low-pass filter and high-pass filter sections of IC9.

The filtered AF signals are amplified at the buffer amplifier

(Q47) and pre-emphasized with +6dB/octave at the pre-

emphasis circuit (C203, R166), and are then applied to the

IDC amplifier section of IC9 (pin 8).

The amplified AF signals are passed through the limitter

amplifier and low-pass filter sections of IC9 after being

passed through the AF mute switch inside of IC9.

The output signals from pin 6 are passed through the splat-

ter filter (IC8) and level controller (IC13, pins 21, 22), and

are then applied to the modulation circuit (D7).

4-2-2 MODULATION CIRCUIT

The modulation circuit modulates the VCO oscillating signal

(RF signal) using the microphone audio signals.

The AF signals from the level controller (IC13) change the

reactance of varactor diode (D7) to modulate the oscillated

signal at the TX VCO circuit (Q12, D8). The modulated VCO

signal is amplified at the buffer amplifiers (Q8, Q6) and is

then applied to the drive amplifier circuit via the T/R switch

(D4).

The CTCSS/DTCS signals from the CPU (IC14, pin 44) are

passed through the low-pass filter (IC21), level controller

(IC13, pins 12, 11) and mixer (IC7), and are then applied to

the VCO circuit via the splatter filter (IC8).