Intel Agilex User manual

Other manuals for Agilex

7

Table of contents

Other Intel Microcontroller manuals

Intel

Intel Quark D2000 User manual

Intel

Intel Agilex 7 FPGA I Series User manual

Intel

Intel Core 2 Duo Processor User manual

Intel

Intel 8XC251SA User manual

Intel

Intel Agilex User manual

Intel

Intel Atom E660 User manual

Intel

Intel Agilex User manual

Intel

Intel Atom N270 User manual

Intel

Intel Cyclone 10 GX FPGA User manual

Intel

Intel 80C196KB Series User manual

Intel

Intel Arria 10 GX User manual

Intel

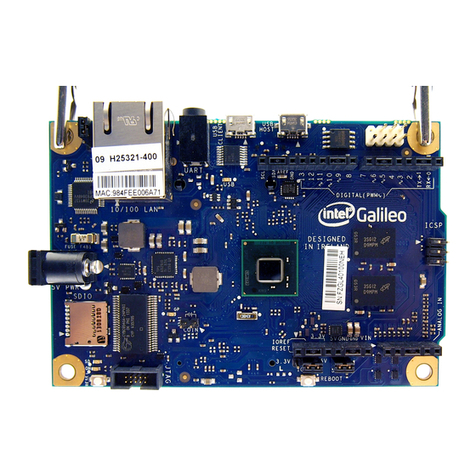

Intel Galileo Operation instructions

Intel

Intel EVI-EM2COMIF User manual

Intel

Intel Agilex User manual

Intel

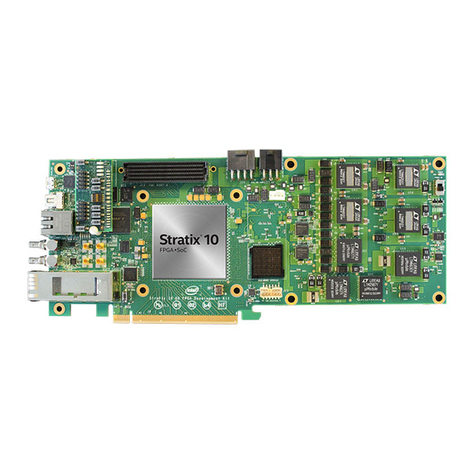

Intel Stratix 10 GX User manual

Intel

Intel Cyclone 10 GX User manual

Intel

Intel Agilex User manual

Intel

Intel Galileo Installation instructions

Intel

Intel Arria 10 series User manual

Intel

Intel Agilex User manual

Popular Microcontroller manuals by other brands

AMS

AMS AS7261 Demo Kit user guide

Novatek

Novatek NT6861 manual

Espressif Systems

Espressif Systems ESP8266 SDK AT Instruction Set

Nuvoton

Nuvoton ISD61S00 ChipCorder Design guide

STMicrolectronics

STMicrolectronics ST7 Assembler Linker user manual

Texas Instruments

Texas Instruments Chipcon CC2420DK user manual

Lantronix

Lantronix Intrinsyc Open-Q 865XR SOM user guide

NEC

NEC 78GK0S/K 1+ Series Application note

Mikroe

Mikroe SEMITECH N-PLC Click Application note

Cypress

Cypress CY4607 HX2VL quick start guide

DIGITAL-LOGIC

DIGITAL-LOGIC MICROSPACE manual

Texas Instruments

Texas Instruments TMS320F2837 D Series Workshop Guide and Lab Manual