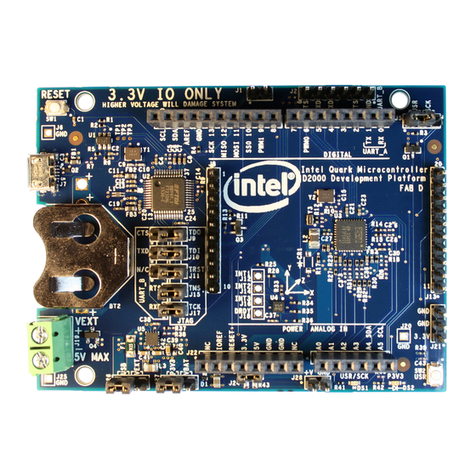

Intel® Quark™ Microcontroller D2000

Platform Design Guide November 2016

4 Document Number: 333580-002EN

11.1 Features .............................................................................................................................................................. 39

12.0 Power Delivery..........................................................................................................................................41

12.1 DVDD Linear Regulator ................................................................................................................................ 41

12.1.1 Operation of an Active Pull –Down Circuit ...................................................................... 41

12.1.2 Implementation of an Active Pull –Down Circuit.......................................................... 41

Figures

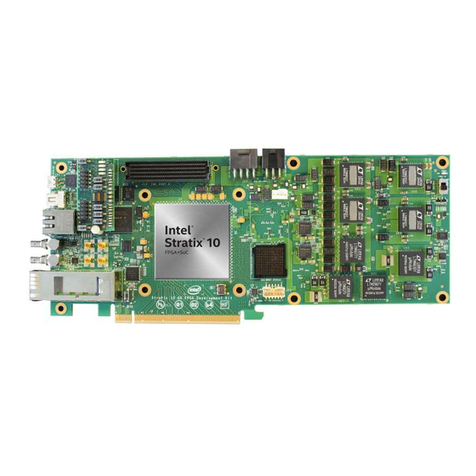

Figure 1. Block Diagram .....................................................................................................................................................9

Figure 2. PCB Floor Plan ................................................................................................................................................. 10

Figure 3. System Diagram .............................................................................................................................................. 11

Figure 4. Single-Ended Microstrip Diagram ........................................................................................................... 12

Figure 5. Differential Microstrip Diagram ................................................................................................................ 13

Figure 6. Backward Coupling Coefficient ................................................................................................................ 14

Figure 7. Forward Coupling Coefficient ................................................................................................................... 14

Figure 8. Single-Ended Kb Diagram........................................................................................................................... 15

Figure 9. Differential Kb Diagram ............................................................................................................................... 15

Figure 10. CRB Pin Mapping Diagram.......................................................................................................................... 17

Figure 11. I²C Interface....................................................................................................................................................... 20

Figure 12. I²C Point-to-Point Topology...................................................................................................................... 21

Figure 13. PWM ..................................................................................................................................................................... 23

Figure 14. Duty Cycle of 20%.......................................................................................................................................... 24

Figure 15. Duty Cycle of 50%.......................................................................................................................................... 24

Figure 16. Duty Cycle of 80%.......................................................................................................................................... 24

Figure 17. UART .................................................................................................................................................................... 26

Figure 18. UART 2-Via Point-to-Point Topology.................................................................................................... 27

Figure 19. SPIO...................................................................................................................................................................... 30

Figure 20. SPI Point-to-Point Single-Ended Topology........................................................................................ 31

Figure 21. RTC........................................................................................................................................................................ 33

Figure 22. RTC Topology................................................................................................................................................... 34

Figure 23. GPIO ..................................................................................................................................................................... 35

Figure 24. GPIO Pin Routing Topology ....................................................................................................................... 36

Figure 25. JTAG Connectivity.......................................................................................................................................... 38

Figure 26. Analog Shielding Requirements .............................................................................................................. 39

Figure 27. Active Pull –Down circuit implementation ......................................................................................... 41

Tables

Table 1. Terminology.........................................................................................................................................................8

Table 2. Reference Documents .....................................................................................................................................8