Smart Socket

User Guide

© 2016-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02046-1.1 3

Figures

Figure 3.1. Smart Socket Programming Board Block Diagram..............................................................................................5

Figure 5.1. Getting Started ...................................................................................................................................................7

Figure 5.2. Scanning..............................................................................................................................................................7

Figure 5.3. Unable to Identify Device ...................................................................................................................................8

Figure 5.4. Identifying Correct Device ..................................................................................................................................8

Figure 5.5. Access Device Properties through Edit ...............................................................................................................8

Figure 5.6. Programming Options.........................................................................................................................................9

Figure 5.7. Bit File Selection .................................................................................................................................................9

Figure 5.8. Program Icon ......................................................................................................................................................9

Figure 5.9. Design Menu.......................................................................................................................................................9

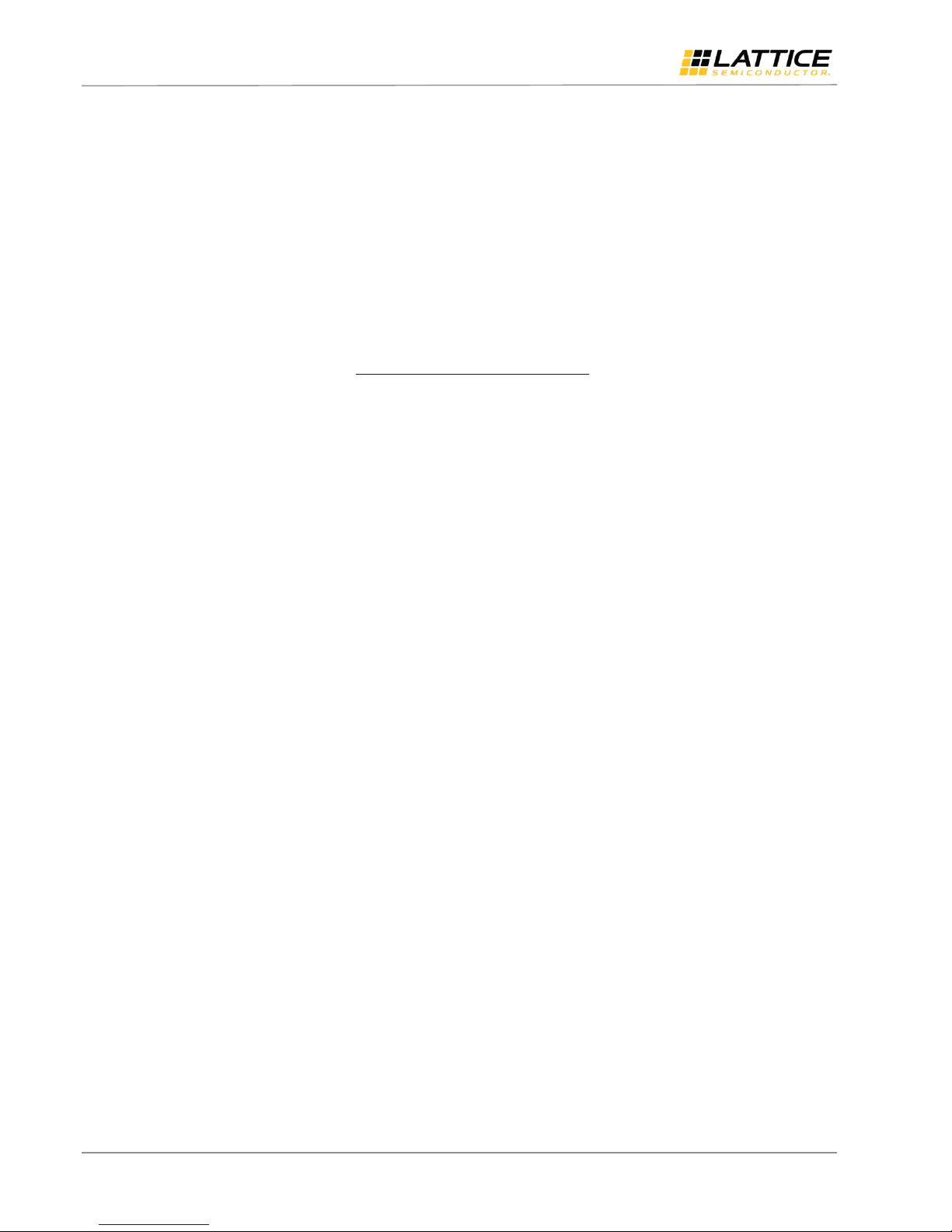

Figure 5.10. Programming in Progress................................................................................................................................10

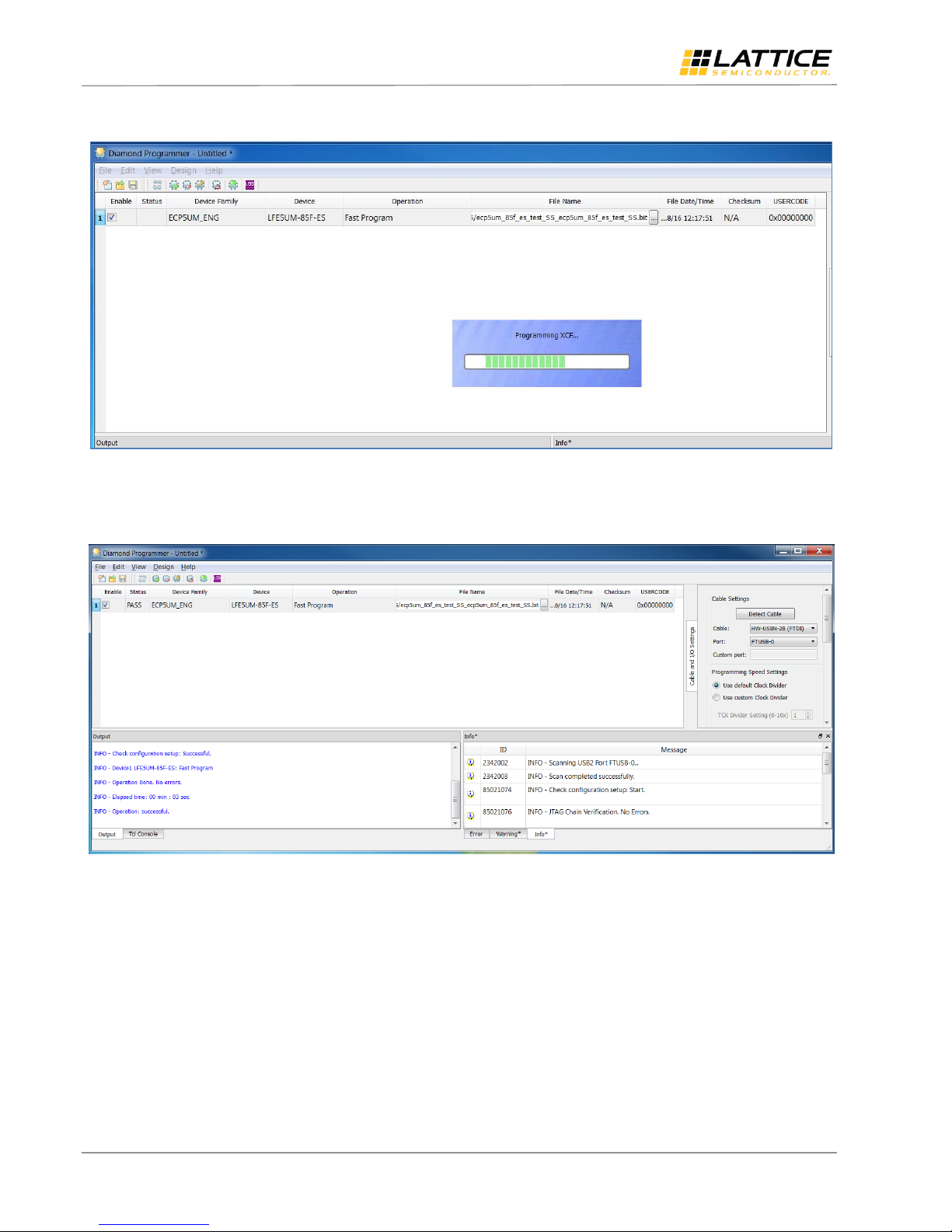

Figure 5.11. Successful Programming.................................................................................................................................10

Figure 5.12. ASC Socket –Scanned MachXO2 Device ........................................................................................................11

Figure 5.13. ASC Socket –Operation ..................................................................................................................................11

Figure 5.14. ASC Socket –Device Properties ......................................................................................................................12

Figure 5.15. ASC Socket –Add External ASC Device ...........................................................................................................12

Figure 5.16. ASC Socket –ASC File Load Menu...................................................................................................................13

Figure 5.17. ASC Socket –Operation Menu........................................................................................................................14

Figure 5.18. Warning ..........................................................................................................................................................14

Figure 5.19. ASC Socket –Warning for MachXO2 ..............................................................................................................15

Figure 5.20. ASC Socket –Ready to Program Step .............................................................................................................15

Figure 5.21. ASC Socket –Programming.............................................................................................................................15

Figure 5.22. ASC Socket –Programming Completed ..........................................................................................................16

Figure 5.23. iCE40 Family –Scanning Failed .......................................................................................................................16

Figure 5.24. iCE40 Family –Device Family List ...................................................................................................................17

Figure 5.25. iCE40 Family –Select the Programming File...................................................................................................17

Figure 5.26. iCE40 Family –Program Icon ..........................................................................................................................17

Figure 5.27. iCE40 Family –Programming Completed Successfully ...................................................................................18

Figure 5.28. CrossLink Family –Scanning Failed.................................................................................................................19

Figure 5.29. CrossLink Family –Device Family List .............................................................................................................20

Figure 5.30. CrossLink Family –Select the Programming File ............................................................................................20

Figure 5.31. CrossLink Family –Program Icon ....................................................................................................................21

Figure 5.32. CrossLink Family –Programming Completed Successfully .............................................................................21

Figure A.1. USB Programming Interface .............................................................................................................................23

Figure A.2. Voltage Regulator and LEDs .............................................................................................................................24

Figure A.3. JTAG Bank and Connections .............................................................................................................................25

Figure A.4. VCC Core, Bypass Caps, and Test Points...........................................................................................................26

Figure B.1. Failed to Scan Device ........................................................................................................................................27

Figure B.2. Detect Cable (FTDI)...........................................................................................................................................27

Figure B.3. Scanning Completed.........................................................................................................................................28