MicroBlaze Debugger and Trace | 3

©1989-2021 Lauterbach GmbH

SYStem.Option.MDMSINGLELMB Use MDM LMB master 0 for all cores 20

TERM.METHOD.MDMUART Terminal configuration 20

Memory Classes 22

Register Names 22

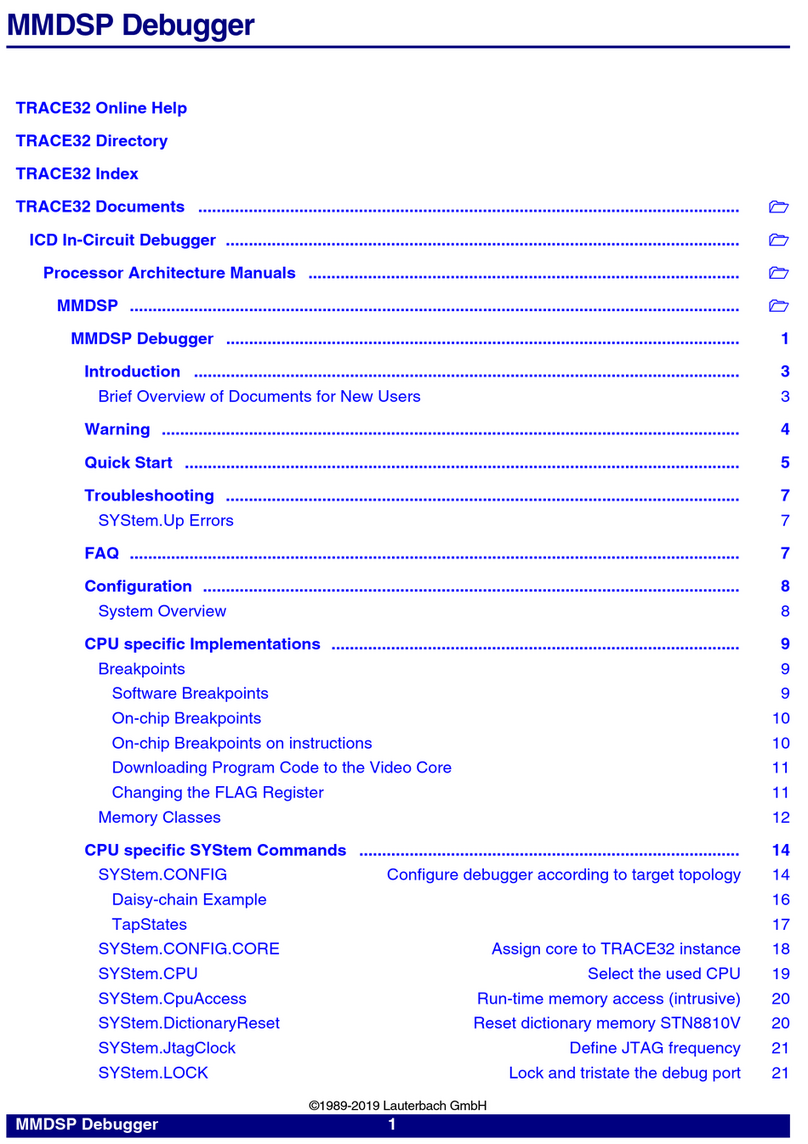

CPU specific SYStem Commands ...................................................................................23

SYStem.CPU Select the used CPU 23

SYStem.JtagClock Selects the frequency for the debug interface 24

SYStem.LOCK Lock and tristate the debug port 24

SYStem.MemAccess Run-time memory access 25

SYStem.Mode Select operation mode 26

SYStem.CONFIG Configure debugger according to target topology 27

Daisy-Chain Example 29

TapStates 30

SYStem.CONFIG.CORE Assign core to TRACE32 instance 31

SYStem.CONFIG.state Display target configuration 32

SYStem.CONFIG.MDM.DebugPort Set core to debug 32

SYStem.CONFIG.MDM.RESet Reset MDM configuration 32

SYStem.CONFIG.MDM.view Display MDM configuration 33

SYStem.CONFIG.MDM.UserInst Set default user BSCAN port 33

TrOnchip Commands ........................................................................................................ 34

TrOnchip.state Display on-chip trigger window 34

TrOnchip.RESet Set on-chip trigger to default state 34

TrOnchip.CONVert Adjust range breakpoint in on-chip resource 34

TrOnchip.VarCONVert Adjust complex breakpoint in on-chip resource 35

CPU specific MMU Commands ........................................................................................ 36

MMU.DUMP Page wise display of MMU translation table 36

MMU.List Compact display of MMU translation table 37

MMU.SCAN Load MMU table from CPU 39

Real-Time Trace ................................................................................................................. 40

SYStem.Option.DTM Control data trace messages 40

SYStem.Option.QUICKSTOP Control trace of software breakpoints 40

Configuring your FPGA .................................................................................................... 41

JTAG Connector ................................................................................................................ 42

Mechanical Description 42

JTAG Connector for Xilinx Microblaze 42