2

M68000 USER’S MANUAL ADDENDUM

MOTOROLA

The primary features of the MC68SEC000 embedded processor include the following:

• Direct Replacement for the MC68EC000

— Pin-for-pin compatibility with the MC68EC000 in the plastic QFP and TQFP packages

— Vast selection of existing third-party development tools for the MC68EC000 support the

MC68SEC000

— Software written for the MC68EC000 will run unchanged on the MC68SEC000

• Power Management

— Low-power HCMOS technology

— Static design allows for stopping the processor clock

— 3.3V or 5V operation

— Typical 0.5

µ

A current consumption at 3.3V in sleep mode

• Software Strength

— Fully upward object-code compatible with other M68000 Family products

— M68000 architecture allows effective assembly code with a C compiler

• Upgrade

— Fully upward code-compatible with higher performance 680x0 and 68300 Family members

— ColdFire

®

code-compatible with minor modifications

1. MC68HC000

The primary benefit of the MC68HC000 is reduced power consumption. The device dissipates less power (by

an order of magnitude) than the NMOS MC68000.

The MC68HC000 is an implementation of the M68000 16/-32 bit microprocessor architecture. The

MC68HC000 has a 16-bit data bus implementation of the MC68000 and is upward code-compatible with the

MC68010 and the MC68020 32-bit implementation of the architecture.

1.1 MC68HC001

The MC68HC001 provides a functional extension to the MC68HC000 HCMOS 16-/32-bit microprocessor with

the addition of statically selectable 8- or 16-bit data bus operation. The MC68HC001 is object-code compatible

with the MC68HC000. You can migrate code written for the MC68HC001 without modification to any member

of the M68000 Family.

1.2 MC68EC000

The MC68EC000 is an economical high-performance embedded controller designed to suit the needs of the

cost-sensitive embedded-controller market. The HCMOS MC68EC000 has an internal 32-bit architecture that

is supported by a statically selectable 8- or 16-bit data bus. This architecture provides a fast and efficient

processing device that can satisfy the requirements of sophisticated applications based on high-level

languages.

The MC68EC000 is fully object-code compatible with the MC68000. You can migrate code written for the

MC68EC000 without modification to any member of the M68000 Family.

The MC68EC000 brings the performance level of the M68000 Family to cost levels previously associated with

8-bitmicroprocessors.The MC68EC000 benefitsfromtherich M68000 instructionsetand its relatedhighcode

density with low memory bandwidth requirements.

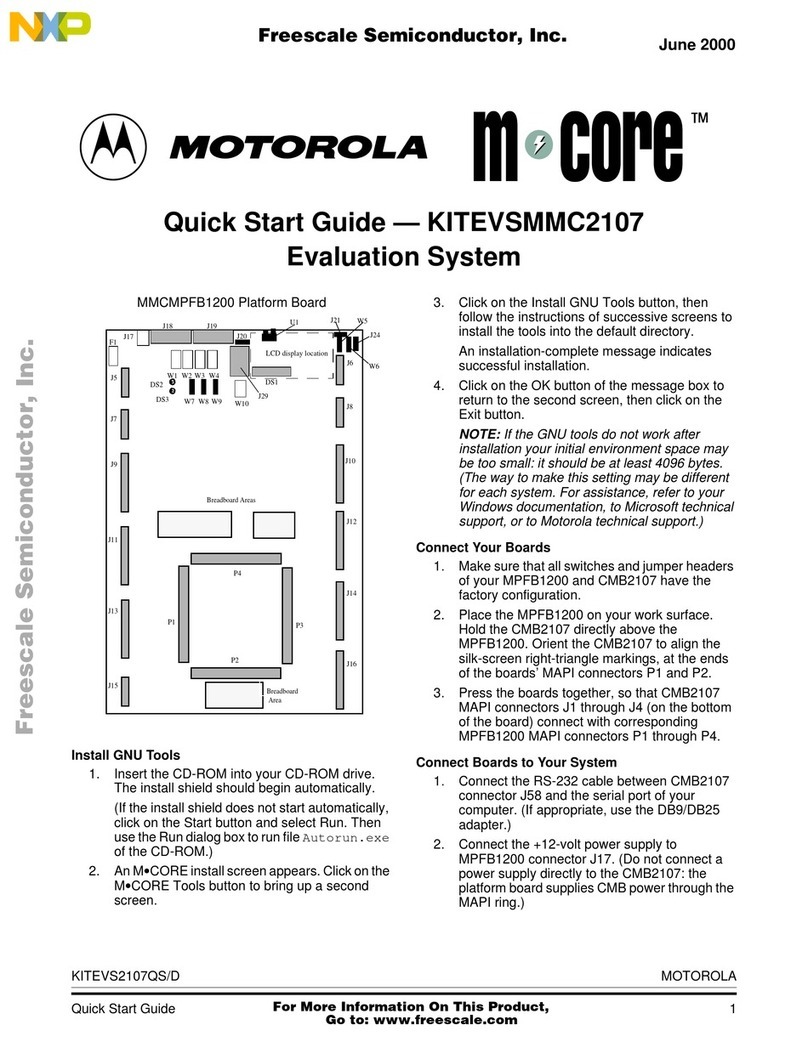

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...