MMC2001 MOTOROLA

REFERENCE MANUAL ix

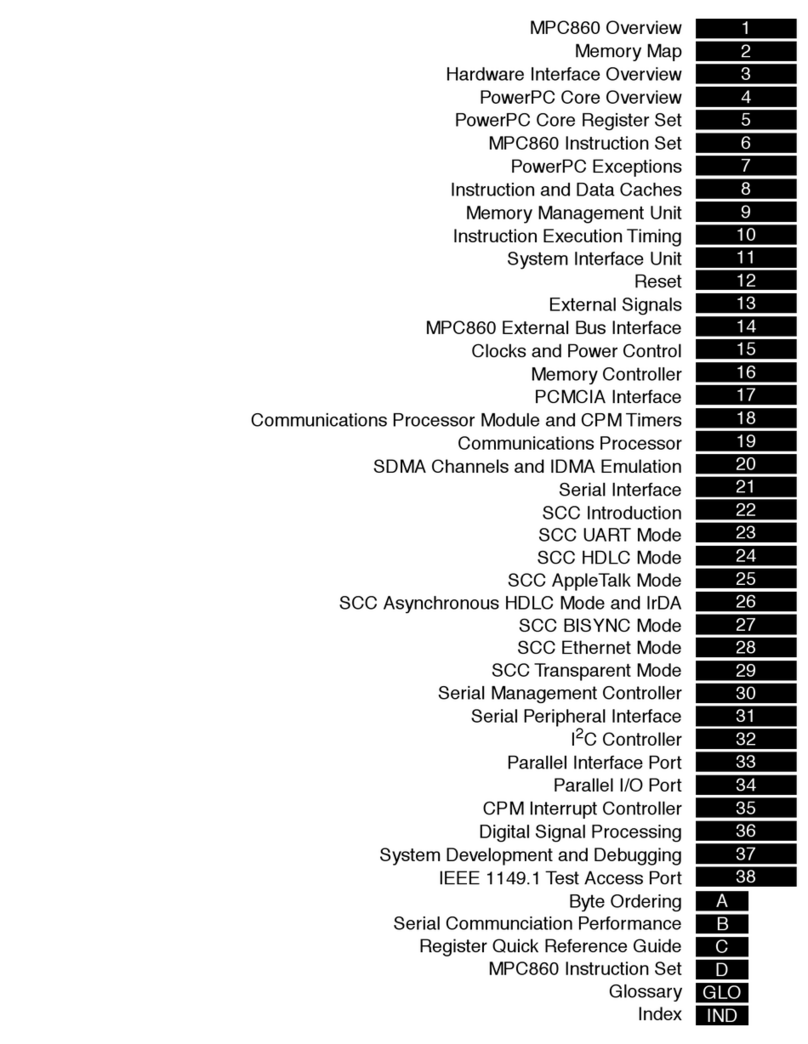

TABLE OF CONTENTS

Paragraph Title Page

SECTION 11

UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER MODULE

11.1 Overview........................................................................................................11-1

11.2 UART Signals.................................................................................................11-2

11.2.1 RTS — Request to Send (UART0)..............................................................11-2

11.2.2 CTS — Clear to Send (UART0) ..................................................................11-2

11.2.3 TXD — UART Transmit...............................................................................11-3

11.2.4 RXD — UART Receive ...............................................................................11-3

11.3 Sub-Block Description....................................................................................11-3

11.3.1 Transmitter..................................................................................................11-3

11.3.2 Receiver......................................................................................................11-3

11.3.3 Infrared Interface.........................................................................................11-4

11.3.4 16x Bit Clock Generator..............................................................................11-4

11.3.5 General UART Definitions...........................................................................11-4

11.4 UART Programming Model............................................................................11-5

11.4.1 UART Receive Register (URX)...................................................................11-7

11.4.2 UART Transmitter Register (UTX) ..............................................................11-8

11.4.3 UART Control Register 1 (UCR1) ...............................................................11-9

11.4.4 UART Control Register 2 (UCR2) .............................................................11-11

11.4.5 UART BRG Register (UBRGR).................................................................11-13

11.4.6 UART Status Register (USR)...................................................................11-14

11.4.7 UART Test Register (UTS)........................................................................11-15

11.5 GPIO Pins and Registers.............................................................................11-16

11.5.1 UART Port Control Register (UPCR) ........................................................11-16

11.5.2 UART Data Direction Register (UDDR).....................................................11-16

11.5.3 UART Port Data Register (UPDR) ............................................................11-17

11.6 Data Sampling Technique on the Receiver..................................................11-17

11.7 UART Operation in Low-Power System Modes...........................................11-23

11.8 UART Operation in System Debug Mode....................................................11-24

SECTION 12

INTERVAL MODE SERIAL PERIPHERAL INTERFACE

12.1 Overview........................................................................................................12-1

12.2 Operation .......................................................................................................12-1

12.2.1 Manual (Master) Mode................................................................................12-2

12.2.2 Interval (Master) Mode................................................................................12-3

12.2.3 Slave Mode .................................................................................................12-3

12.3 Signal Descriptions ........................................................................................12-3

12.3.1 SPI_MISO (Master In, Slave Out) ...............................................................12-3

12.3.2 SPI_MOSI (Master Out, Slave In)...............................................................12-4

12.3.3 SPI_EN........................................................................................................12-4

12.3.4 SPI_CLK......................................................................................................12-4

12.3.5 SPI_GP .......................................................................................................12-4

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...