PRELIMINARY

Contents

Paragraph

Number Title Page

Number

vi MPC533 Reference Manual MOTOROLA

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

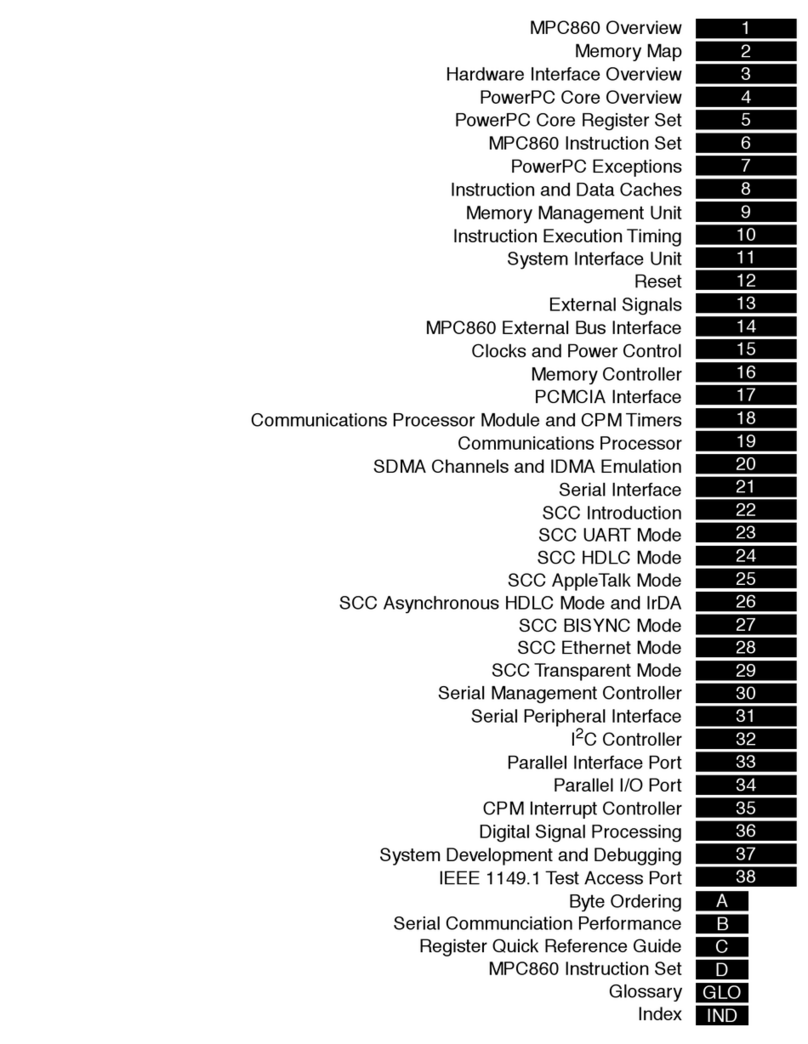

3.13.7 Branch Instructions........................................................................................ 3-43

3.13.7.1 Invalid Branch Instruction Forms.............................................................. 3-43

3.13.7.2 Branch Prediction ...................................................................................... 3-44

3.13.8 Fixed-Point Processor.................................................................................... 3-44

3.13.8.1 Fixed-Point Instructions............................................................................. 3-44

3.13.9 Floating-Point Processor................................................................................ 3-45

3.13.9.1 General....................................................................................................... 3-45

3.13.9.2 Optional instructions.................................................................................. 3-45

3.13.10 Load/Store Processor..................................................................................... 3-45

3.13.10.1 Fixed-Point Load With Update and Store With Update Instructions ........ 3-45

3.13.10.2 Fixed-Point Load and Store Multiple Instructions .................................... 3-45

3.13.10.3 Fixed-Point Load String Instructions.........................................................3-45

3.13.10.4 Storage Synchronization Instructions........................................................ 3-45

3.13.10.5 Floating-Point Load and Store With Update Instructions .........................3-46

3.13.10.6 Floating-Point Load Single Instructions.................................................... 3-46

3.13.10.7 Floating-Point Store Single Instructions.................................................... 3-46

3.13.10.8 Optional Instructions ................................................................................. 3-46

3.14 Virtual Environment Architecture (VEA).......................................................... 3-46

3.14.1 Atomic Update Primitives ............................................................................. 3-46

3.14.2 Effect of Operand Placement on Performance .............................................. 3-47

3.14.3 Storage Control Instructions..........................................................................3-47

3.14.4 Instruction Synchronize (isync) Instruction................................................... 3-47

3.14.5 Enforce In-Order Execution of I/O (eieio) Instruction.................................. 3-47

3.14.6 Time Base ...................................................................................................... 3-47

3.15 Operating Environment Architecture (OEA)..................................................... 3-47

3.15.1 Branch Processor Registers ........................................................................... 3-48

3.15.1.1 Machine State Register (MSR)..................................................................3-48

3.15.1.2 Branch Processors Instructions.................................................................. 3-48

3.15.2 Fixed-Point Processor.................................................................................... 3-48

3.15.2.1 Special Purpose Registers.......................................................................... 3-48

3.15.3 Storage Control Instructions..........................................................................3-48

3.15.4 Exceptions...................................................................................................... 3-48

3.15.4.1 System Reset Exception and NMI (0x0100)............................................. 3-49

3.15.4.2 Machine Check Exception (0x0200)......................................................... 3-50

3.15.4.3 Data Storage Exception (0x0300).............................................................. 3-51

3.15.4.4 Instruction Storage Exception (0x0400).................................................... 3-52

3.15.4.5 External Interrupt (0x0500)....................................................................... 3-52

3.15.4.6 Alignment Exception (0x00600) ............................................................... 3-53

3.15.4.7 Program Exception (0x0700)..................................................................... 3-55

3.15.4.8 Floating-Point Unavailable Exception (0x0800)....................................... 3-56

3.15.4.9 Decrementer Exception (0x0900).............................................................. 3-57