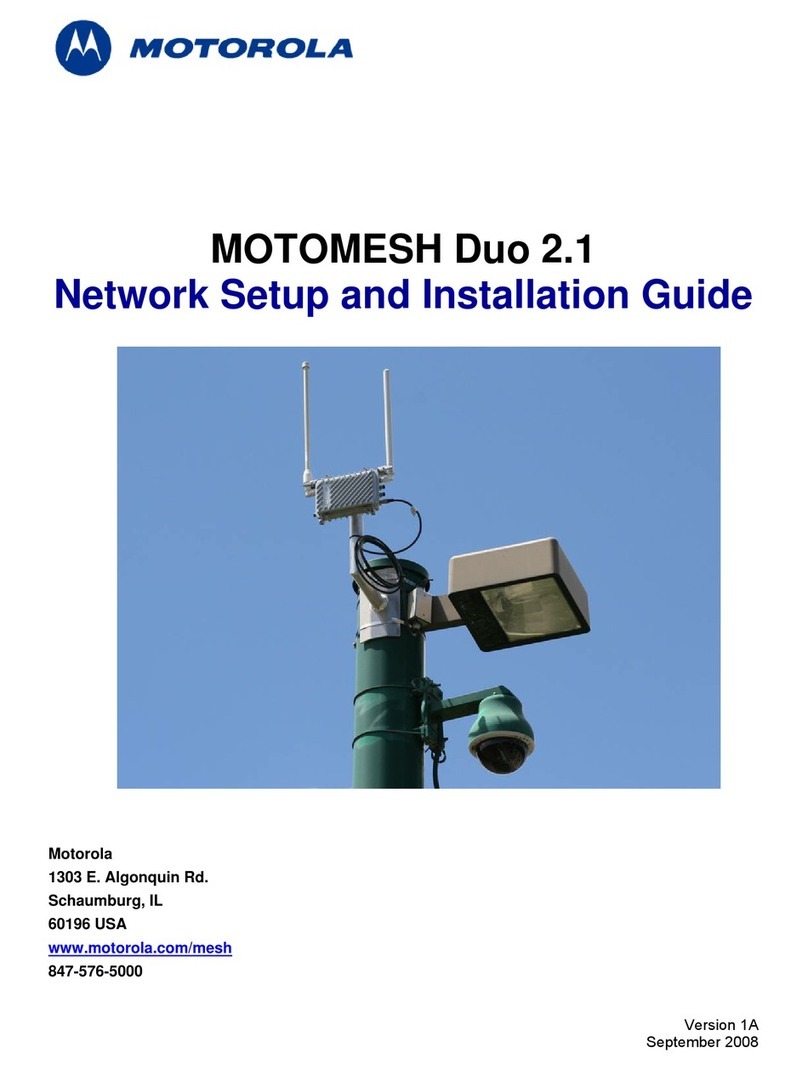

Motorola M68MM01 User manual

Other Motorola Network Hardware manuals

Motorola

Motorola MOTOMESH DUO 4300 User manual

Motorola

Motorola VAP2404 User manual

Motorola

Motorola PTP 500 User manual

Motorola

Motorola Avigilon HD-NVR4-PRM-64TB User manual

Motorola

Motorola DIMETRA MTS 2 User manual

Motorola

Motorola CB3000 - Client Bridge - Wireless Access... User manual

Motorola

Motorola AT Commands G24-L Instruction Manual

Motorola

Motorola CPEi 725 User manual

Motorola

Motorola PMP 58430 User manual

Motorola

Motorola Canopy Powerline MU User manual

Motorola

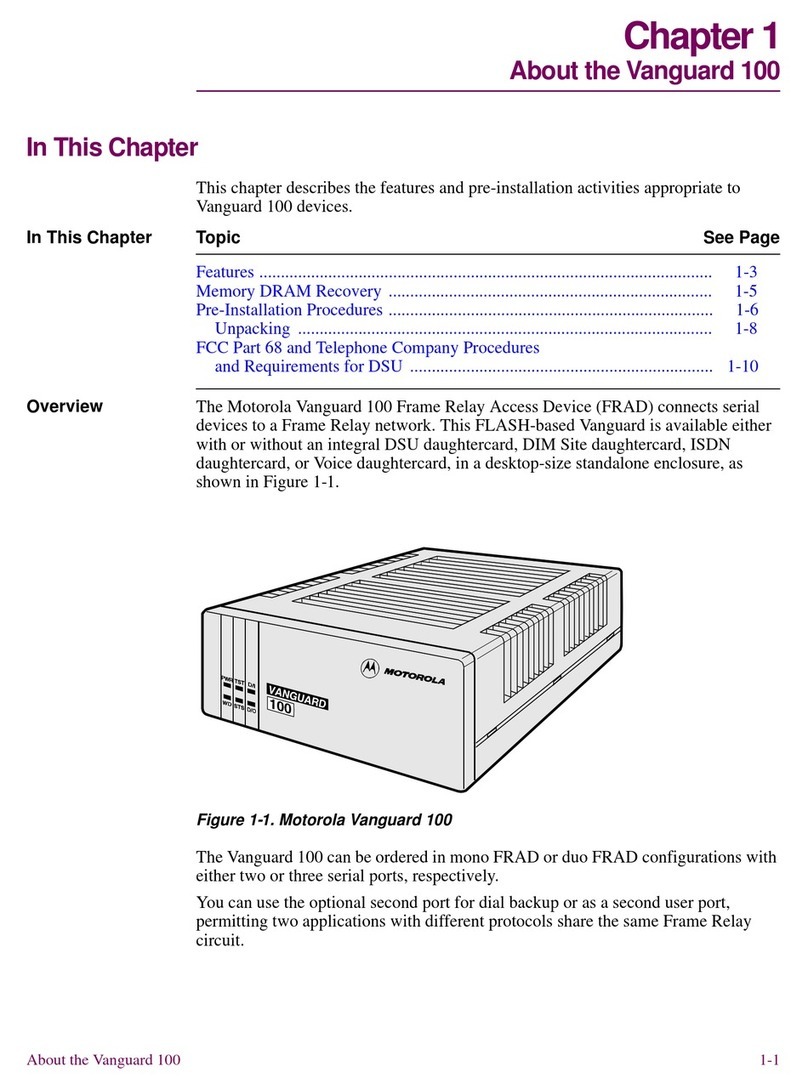

Motorola 68436 - Vanguard 100I - Remote Access Server Manual

Motorola

Motorola Dimetra KVL 4000 Air User manual

Motorola

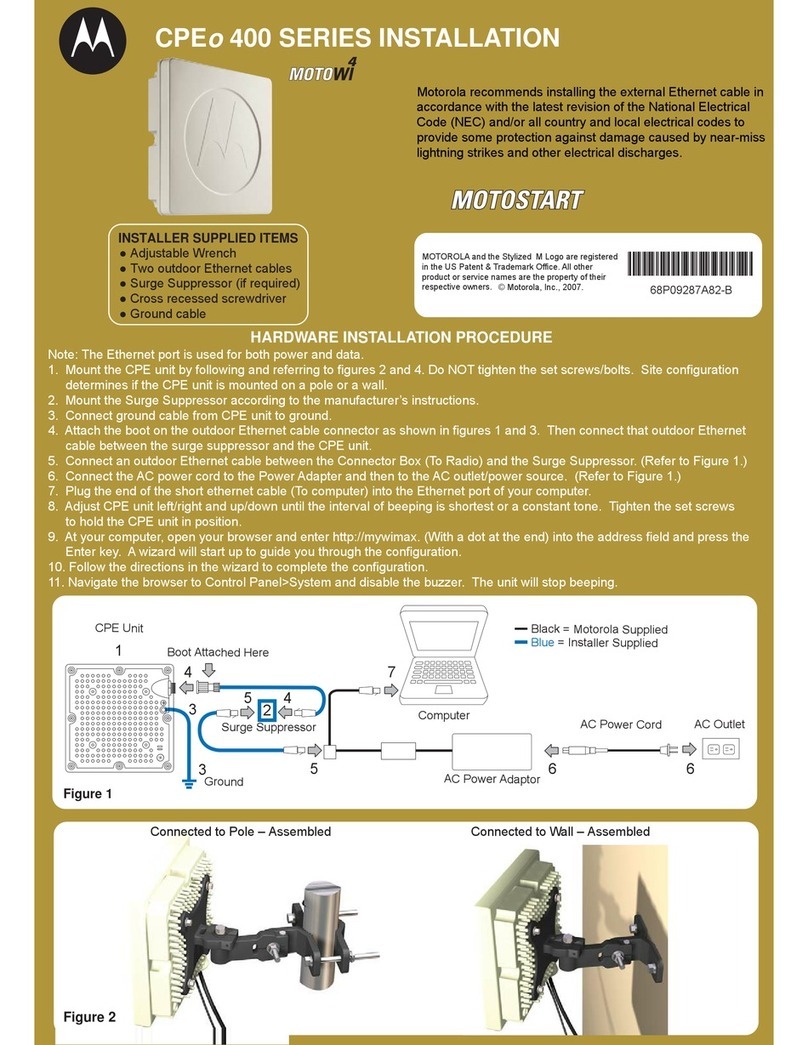

Motorola PMP 400 User manual

Motorola

Motorola MotoWI4 PTP 600 Series User manual

Motorola

Motorola Avigilon HD-NVR4-STD-16TB User manual

Motorola

Motorola M68ICS08RK User manual

Motorola

Motorola CPEi 825 Series Owner's manual

Motorola

Motorola Starline SG 2000 User manual

Motorola

Motorola vap2400 User manual

Motorola

Motorola 2.1 User manual

Popular Network Hardware manuals by other brands

Matrix Switch Corporation

Matrix Switch Corporation MSC-HD161DEL product manual

B&B Electronics

B&B Electronics ZXT9-IO-222R2 product manual

Yudor

Yudor YDS-16 user manual

D-Link

D-Link ShareCenter DNS-320L datasheet

Samsung

Samsung ES1642dc Hardware user manual

Honeywell Home

Honeywell Home LTEM-PV Installation and setup guide