1508i(RM-430)

Baseband Description and Troubleshooting

Nokia Customer

Care

Issue 1

Copyright © 2008 Nokia, All rights reserved

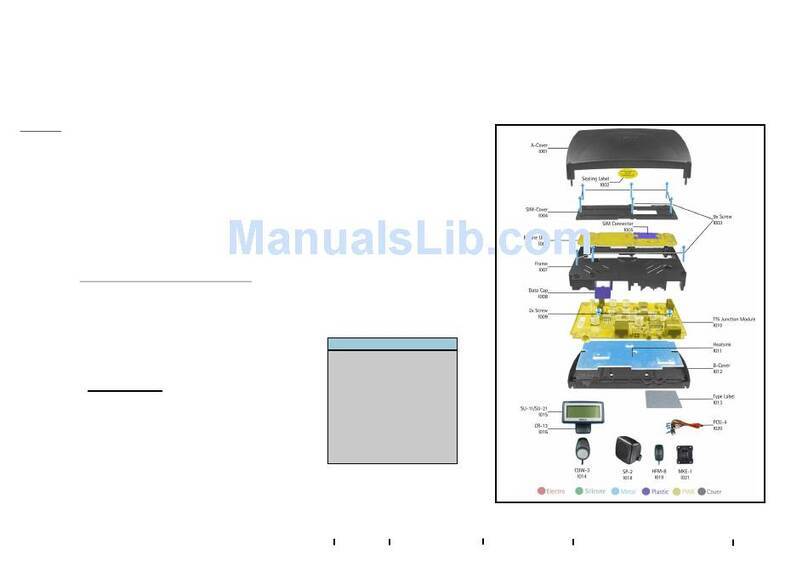

The interface of the CBP5.6 is described in the following

diagram. Receive and transmit interfaces for CBP 5.6

provide analog I and Q signals and support super-

heterodyne radio and direct conversion radio design. The

CP external-memory interface supports 3.0V or 1.8V, the

address bus supports 16-bit address which can support

three to six external devices via chip selects. CBP 5.6

includes 48 GPIOs and interrupts, some of which are

multiplexed with other functions. All GPIO pins are in input

state by default and use a large pull-up or pull-down resistor

value to minimize the current drain. The USB port supports

data rates of up to 12Mbps, the USB analog drivers and

48.00MHz PLL are integrated into CBP 5.6, the control

processor manages the USB function. Two independent

serial-peripheral interfaces are provided on CBP 5.6: one is

for RF control and the other is for general-purpose use. The

R-UIM interface supports 3V UIM cards and consists of five

pins, these pins are multiplexed with another function. The

CP manages the R-UIM function.

Five independent PDM DACs are supplied on the CBP 5.6

chip.

Three of the outputs are dedicated to radio-control signals

for Rx automatic gain control (AGC), Tx AGC, and automatic

frequency control (AFC). The fourth and fifth PDM outputs

are spares. The PDMs are 12-bit DACs and have a

guaranteed output range of 0.2 V to 2.5 V.

The 12-bit auxiliary ADC supports eight independent

external channels on pins AUXADC [7:0]. There are also

eight internal channels used to measure internal analog

voltages. The input voltage range is 0.2 V to 2.7 V. The

conversion time is 156 µsec. The typical uses of the external