NVIDIA Jetson TX2 NX DG-10141-001_v1.1 | v

List of Figures

Figure 2-1. Jetson TX2 NX Block Diagram...............................................................................5

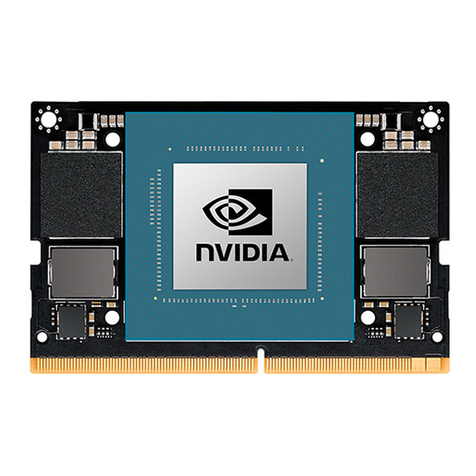

Figure 4-1. Jetson TX2 NX Module Installed in SODIMM Connector......................................9

Figure 4-2. Module to Connector Assembly Diagram ...........................................................10

Figure 5-1. Jetson TX2 NX Power and Control Block Diagram ............................................12

Figure 5-2. System Power and Control Block Diagram........................................................14

Figure 5-3. Power Up Sequence (No Power Button – Auto Power-On) ...............................14

Figure 5-4. Power-Up Sequence (With Power Button)..........................................................15

Figure 5-5. Power Down – Initiated by SHUTDOWN_REQ* Assertion..................................15

Figure 5-6. Power Down – Sudden Power Loss ....................................................................15

Figure 6-1. USB Connection Example....................................................................................18

Figure 6-2. IL/NEXT Plot .........................................................................................................21

Figure 6-3. Trace Spacing for TX/RX Non-Interleaving.........................................................21

Figure 6-4. Via Structures.......................................................................................................22

Figure 6-5. ESD Layout Recommendations...........................................................................22

Figure 6-6. Component Order.................................................................................................22

Figure 6-7. Example PCIe Connections..................................................................................24

Figure 6-8. AC Cap Voiding .....................................................................................................26

Figure 6-9. Jetson TX2 NX Ethernet Connections .................................................................28

Figure 6-10. Gigabit Ethernet Magnetics and RJ45 Connections...........................................28

Figure 7-1. DSI 1 x 2 Lane Connection Example....................................................................31

Figure 7-2. DP and eDP Connection Example on DP0 Pins..................................................34

Figure 7-3. eDP Differential Main Link Topology...................................................................34

Figure 7-4. S-parameter .........................................................................................................37

Figure 7-5. Via Topology #1 ....................................................................................................37

Figure 7-6. Via Topology #2 ....................................................................................................37

Figure 7-7. HDMI Connection Example..................................................................................38

Figure 7-8. HDMI CLK and Data Topology .............................................................................39

Figure 7-9. IL and FEXT Plot ...................................................................................................42

Figure 7-10. TDR Plot................................................................................................................42

Figure 7-11. HDMI Via Topology ...............................................................................................43

Figure 7-12. Add-on Components – Top ..................................................................................43

Figure 7-13. Add-on Components – Bottom ............................................................................43

Figure 7-14. AC Cap Void ..........................................................................................................43

Figure 7-15. RPD, Chock, FET Placement ...............................................................................43

Figure 7-16. ESD Footprint .......................................................................................................44

Figure 7-17. ESD Void................................................................................................................44

Figure 7-18. SMT Pad Trace Entering ......................................................................................44