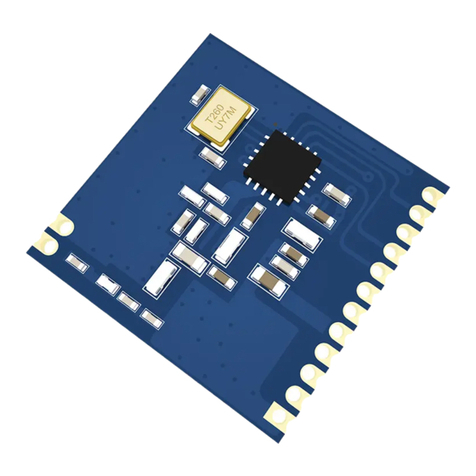

RF-BM-2652P2(I)

www.szrfstar.com V1.1 - May, 2023

Shenzhen RF-star Technology Co., Ltd. Page 2 of 24

1 Device Overview

1.1 Description

RF-BM-2652P2(I) is an RF module based on TI lower-power CC2652P SoC, which is a multiprotocol 2.4 GHz wireless

module supporting Thread, Zigbee®, Bluetooth®5.3 Low Energy, IEEE 802.15.4, IPv6-enabled smart objects

(6LoWPAN), proprietary systems, including the TI 15.4-Stack (2.4 GHz), and concurrent multiprotocol through a

Dynamic Multiprotocol Manager (DMM) driver. It integrates a 48 MHz crystal and a 32.768 kHz crystal, 352 KB of

in-system Programmable Flash, 256 KB ROM, 8 KB of Cache SRAM, and 80 KB of ultra-low leakage SRAM. Its ARM®

Cortex®-M4F core application processor can operate at an extremely low current at flexible power modes. And the

module enables long-range and low-power applications using an integrated +20 dBm high-power amplifier with

best-in-class transmit current consumption at 85 mA. It features a small size, robust connection distance, and rigid

reliability. Optional antenna output modes (PCB, IPEX connector, and half-hole interface) make the module more

convenient for application and development.

1.2 Key Features

•RF Section

- Bluetooth 5.3 Low Energy

- ZigBee, Thread

- IEEE 802.15.4

- IPv6-nabld smart objects (6LoWPAN)

- Proprietary systems

- SimpleLinkTM TI 15.4-Stack (2.4 GHz)

- Dynamic Multiprotocol Manager (DDM) driver

•TX power: up to +20 dBm with temperature

compensation

•Excellent receiver sensitivity

- -105 dBm for Bluetooth 125 kbps (LE coded PHY)

- -100 dBm for 802.15.4 (2.4 GHz)

•Wide Operation Range

- 1.8 V to 3.8 V single power supply

- Operating temperature: -40 °C to +85 °C

- Storage temperature: -40 °C to +125 °C

•Microcontroller

- Powerful 48 MHz ARM®Cortex®-M4F processor

- EEBMC CoreMark®score: 148

- 2-pin cJTAG and JTAG debugging

- Support OTA upgrade

•Memory

- 352 KB of in-system programmable flash

- 256 KB of ROM for protocols and library

functions

- 8 KB of cache SRAM (Alternatively available as

general-purpose RAM)

- 80 KB of ultra-low leakage SRAM. The SRAM is

protected by parity to ensure high reliability of

operation.

•Ultra-low power sensor controller with 4 KB of

SRAM

- Sample, store, and process sensor data

- Operation independent from system CPU

- Fast wake-up for low-power operation

•Rich Peripherals

- 23 GPIOs, digital peripheral pins can be routed

to any GPIOs

- 4 ×32-bit or 8 × 16-bit general-purpose timers

- 12-bit ADC, 200 kSamples/s, 8 channels

- 2 × comparators with internal reference DAC (1

× continuous time, 1 × ultra-low power)

- Programmable current source