Rohm LAPIS Semiconductor ML22660 User manual

Other Rohm Computer Hardware manuals

Rohm

Rohm PMIC BD96801 User manual

Rohm

Rohm BU1570KN Specification sheet

Rohm

Rohm BD16950EFV-EVK-001 User manual

Rohm

Rohm BD9P108MUF-TSB-001 User manual

Rohm

Rohm BP35C5 User manual

Rohm

Rohm BD7682FJ-EVK-301 User manual

Rohm

Rohm REFLED005-EVK-002 User manual

Rohm

Rohm LAPIS Semiconductor ML62Q1739 User manual

Rohm

Rohm LAPIS Semiconductor ML7404 Series Guide

Rohm

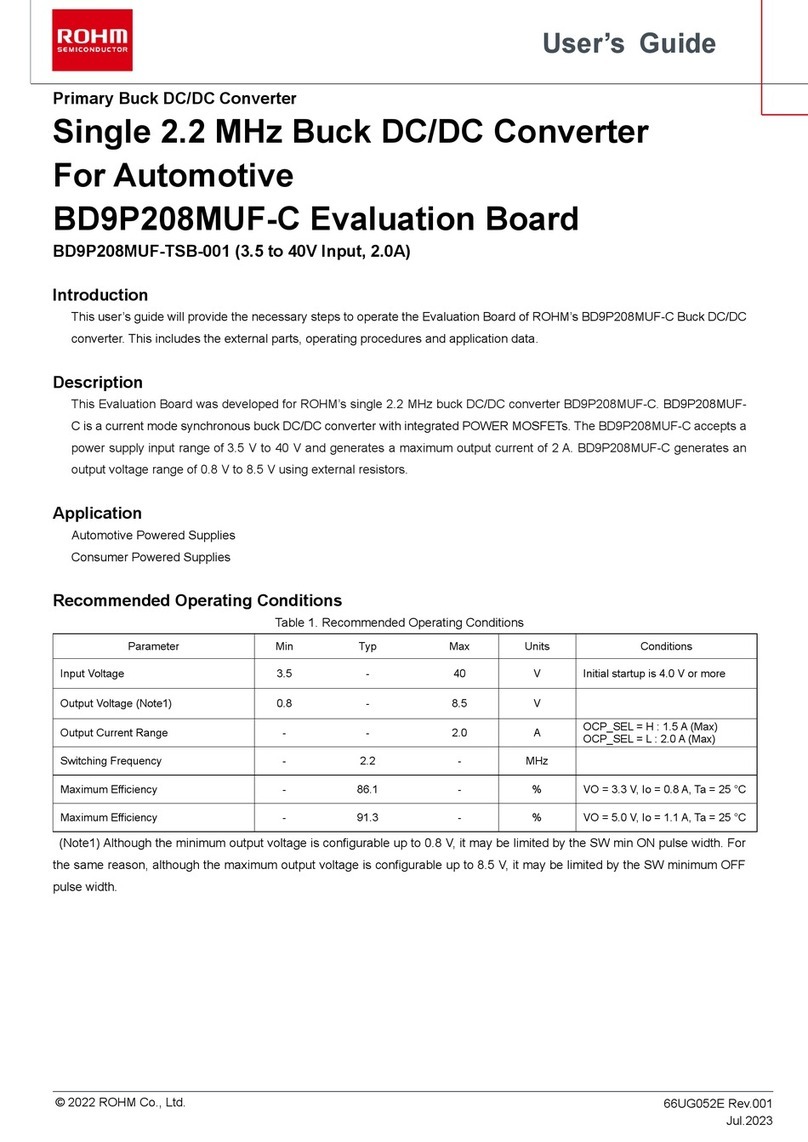

Rohm BD9P208MUF-TSB-001 User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual