SAMSUNG Proprietary-Contents may change without notice

ThisDocumentcan notbe used withoutSamsung'sauthorization

CircuitDescription

2-4

Forthepurposeofenabling YMU765_MA5to demonstarteitsfull capablities,Yamahapurposeto use"SMAF:Synthetic

musicMobileApplication Format"asadatadistribution format that iscompatiblewihtmultimedia.Since theSMAFtakes

astructurethatsetsimportance on thesynchronization betweensound and images,variouscontentscan bewrittenintoit

including incoming call melody withwordsthatcan beusedfortraning karaoke,and commercialchannel thatcombines

texts,imagesand sounds,and others.ThehardwaresequencerofYMU765_MA5 directlyinterpretsand playsblocks

relevant tosysthesis(playing music and reproducing ADPCMwithFMsynthesizer) thatareincludedin datadistributedin

SMAF.

9.Memory

SignalsintheOM6359 enabletwomemories.They useonly onevolt supply voltage,VDD3inthePCF50601.This

systemusesSamsung'smemory,KBB06B400M-F402.It isconsisted of128MbitsflashNORmemoryand 256Mbits

flashNAND memoryand 64MbitsSCRAM.Ithas16 bit dataline,HD[0~15]whichisconnectedtoOM6359 and

MV317SAQ.Ithas26 bit address lines,HA[1~26].CS_NAND and NCSRAMsignalsischipselect.Writing process,

HWR_Nislowand it enableswriting process toflashmemoryand SRAM.During reading process,HRD_Nislowand

it enablesreading process toflashmemoryand SRAM.EachchipselectsignalsintheOM6359 selectmemoryamong 2

flashmemoryand SCRAM.Reading orwriting procedureisprocessedafterHWR_NorHRD_Nisenabled.Memories

usereset,whichisVDD3 delayfromPCF50601.HA[25]signalenableslowerbyteofSRAMand HA[26]signalenables

higherbyteofSRAM.

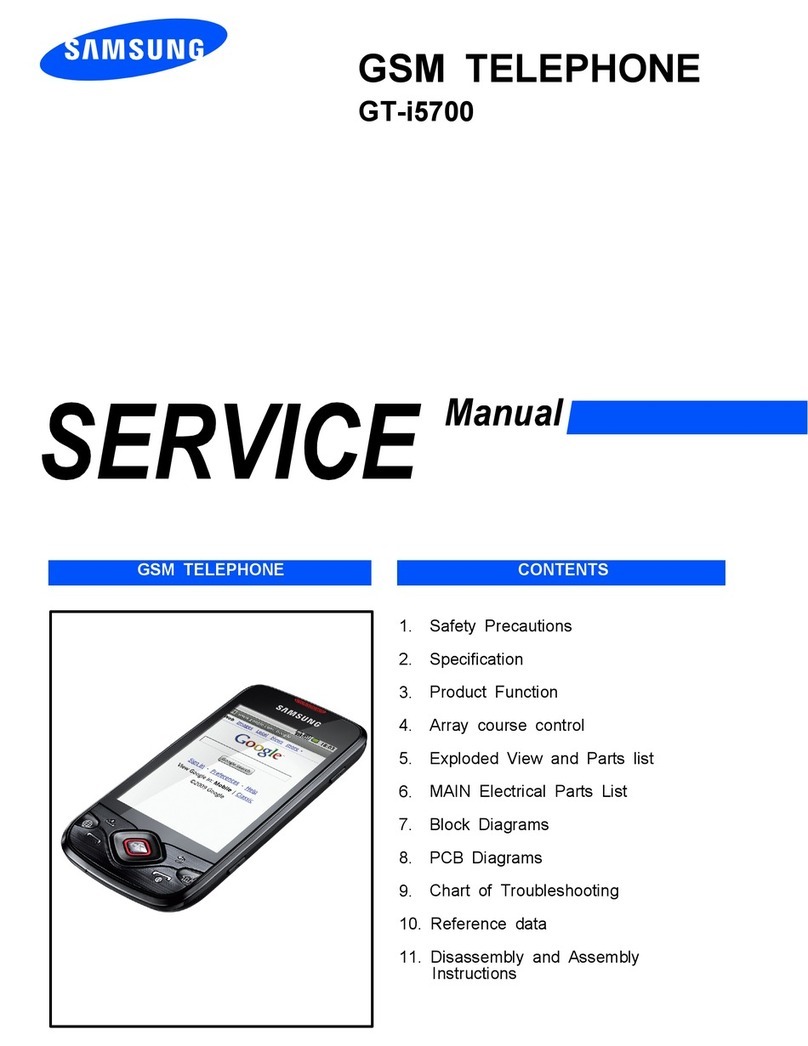

10.OM6359

OM6359 isconsisted ofARMcore and DSP core.Ithas8x1Kword on-chip program/dataRAM,55 Kwordson-chip

programROMintheDSP.Ithas4K*32bitsROMand 2K*32bitsRAMintheARMcore.DSP isconsisted ofKBS,

JTAG,EMIand UART.ARMcoreisconsisted ofEMI,PIC(ProgrammableInterruptController),reset/power/clock unit,

DMAcontroller,TIC(TestInterface Controller),peripheralbridge,PPI,SSI(SynchronousSerialInterface),

ACC(Asynchronouscommunicationscontrollers),timer,ADC,RTC(Real-TimeClock)and keyboardinterface.

KBIO(0:7),address linesofDSP core and HD[0~15].HA[1~26],address linesofARMcore and HD[0~15],datalinesof

ARMcore are connectedtomemory,YMU765,MV317SAQ(CameraDSP Chip).

CS_NAND,NCSRAM,NCSFLASHintheARMcore are connectedtoeachmemory.HWR_Nand HRD_Ncontrol the

process ofmemory.ExternalIRQ(InterruptReQuest)signalsfromeach units,suchasPMU,needthe compatibleprocess.

KBIO[0~7] receivethestatusfromkeyand RXD0/TXD0/irDA_DOWNareusedforthe communicationsusing IRDA and

datalink cable(DEBUG_DTR/RTS/TXD/RXD/CTS/DSR).

Ithas JTAG controlpins(TDI/TDO/TCK) forARMcore and DSP core.Itrecieves13MHz clockinCKIpinfromexternal

TCXO.ADC(Analog toDigitalConvertor) partreceivesthestatusoftemperature,batterytype and battery voltage.

11.VC-TCXO-214C6(26MHz)

This systemusesthe26MHzTCXO.AFCcontrolsignalformsOM6359 controlfrequencyfrom26MHzx-tal.Itgenerates

the clockfrequency.ThisclockisconnectedtoUAA3536.