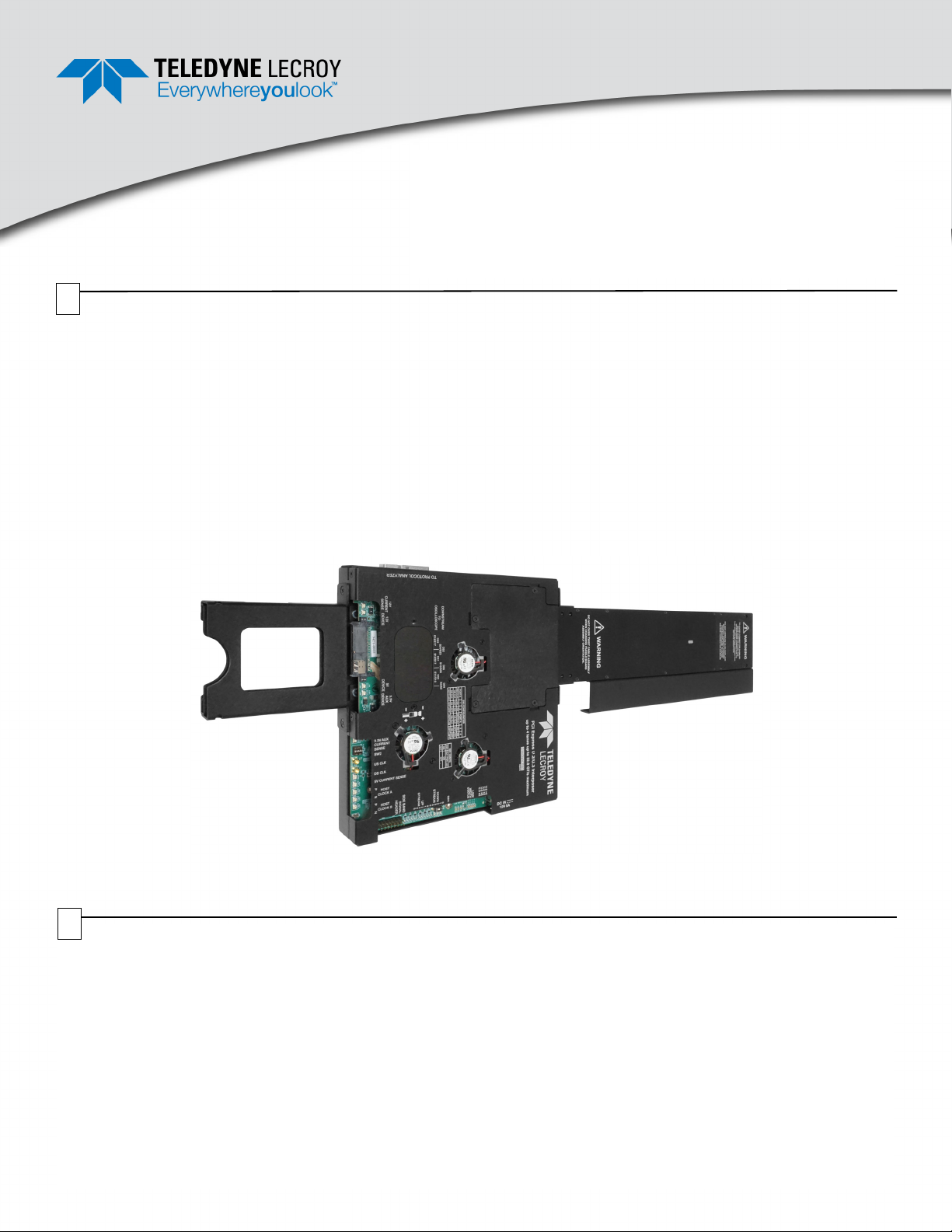

PCI Express®5.0 U.2/U.3 12 Inch

Interposer CrossSync PHY Capable

User Manual and Quick Start Guide

Use this document for quick installation and setup.

Components

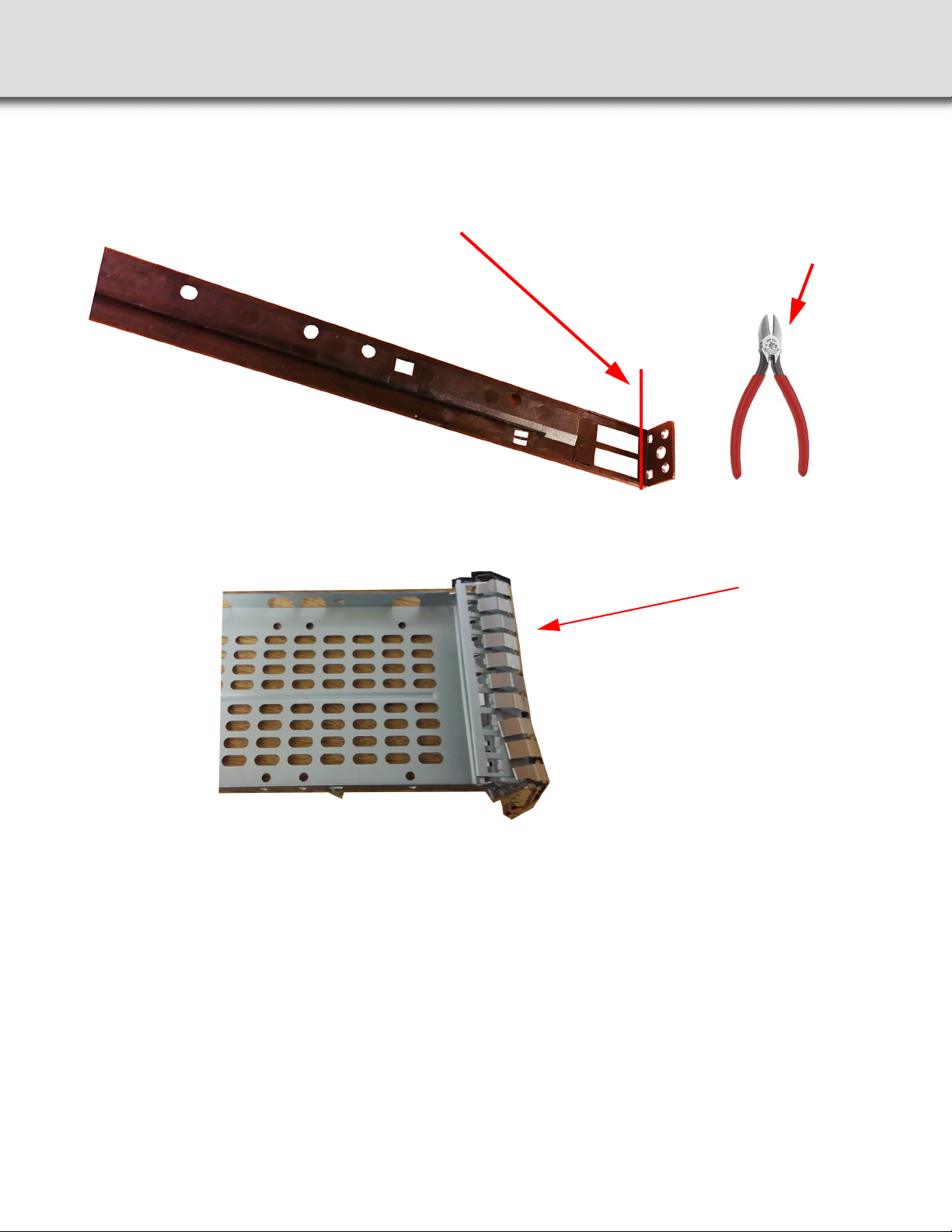

The interposer package includes the following components:

• PCI Express 5.0 U.2/U.3 12 inch Interposer

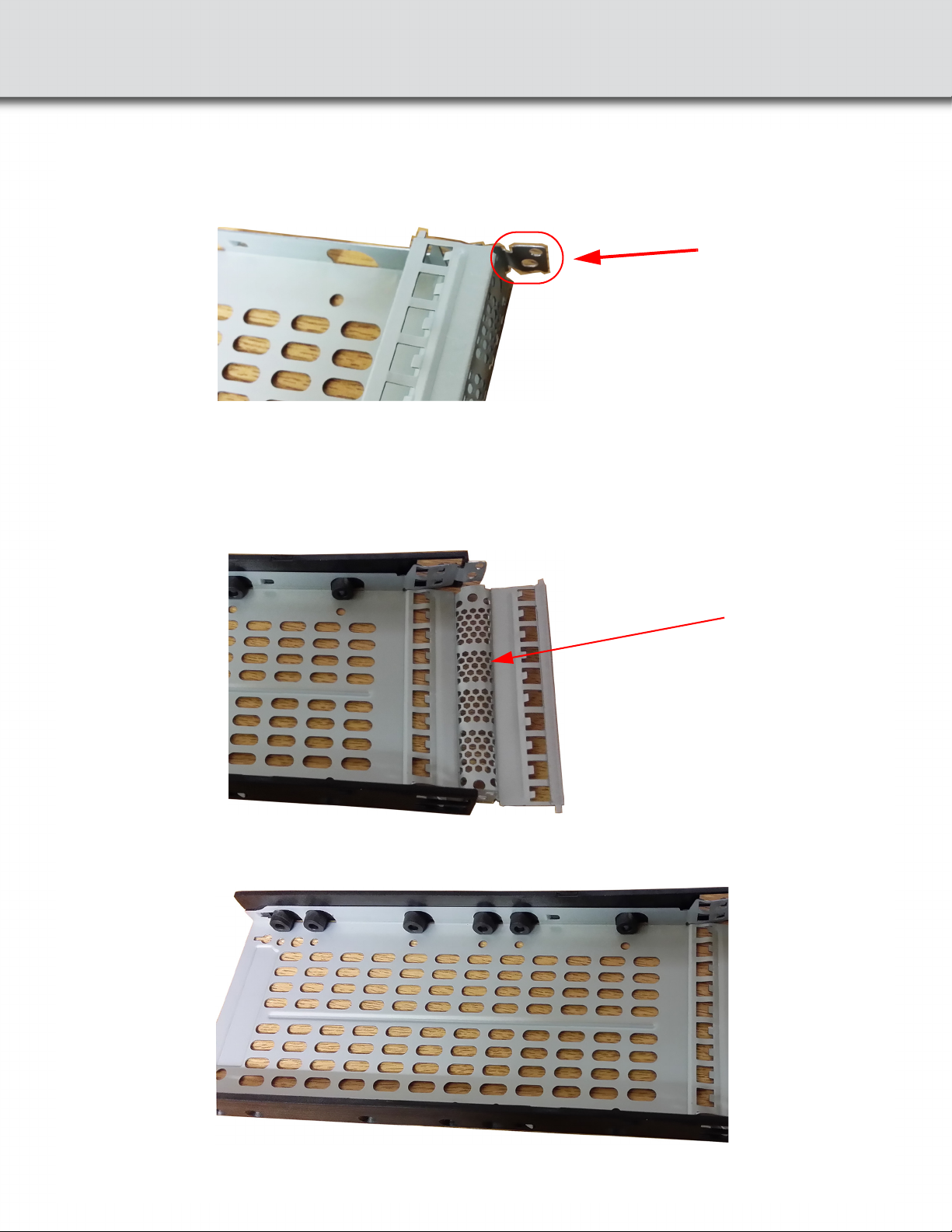

• 3.5 Inch conversion bracket and screws

• Two 90 degree conversion brackets and screws

• Support bracket for 7mm DUT and screws

• DC Power Adapter (+12V @ 5A)

• User Manual and Quick Start Guide (this document)

Inspect the received shipping container for any damage. Unpack the container and account for each of the system

components listed on the accompanying packing list. Visually inspect each component for absence of damage. In the

event of damage, notify the shipper and Teledyne LeCroy. Retain all shipping materials for shipper’s inspection.

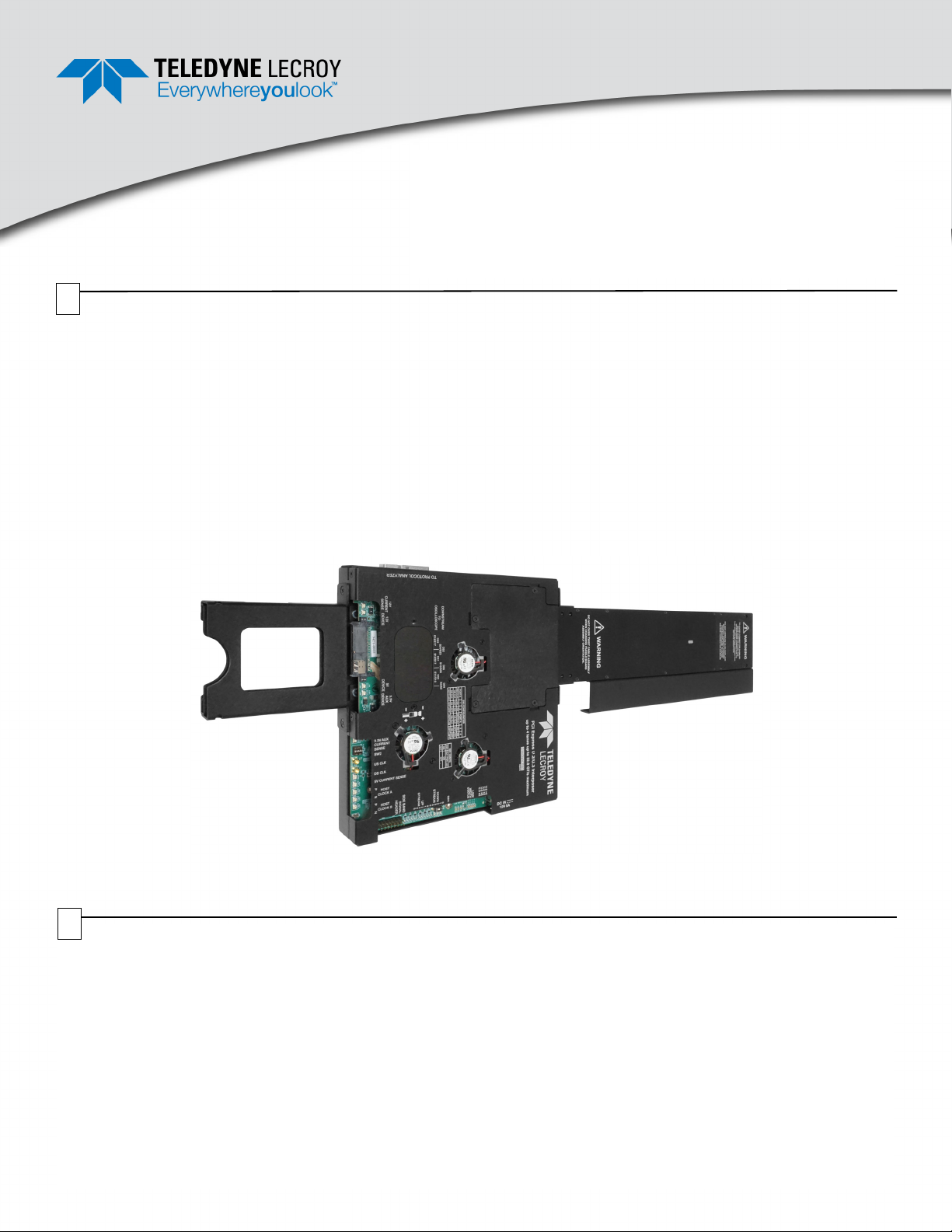

Introduction

Teledyne LeCroy’s PCI Express 5.0 U.2/U.3 12 inch Interposer provides a quick and simple means for protocol analysis

of Solid State Drives (SSDs) based on PCI Express (PCIe®) protocols. The U.2/U.3 Interposer, used with a Summit

Protocol Analyzer, enables PCIe bus traffic between a host backplane and SSD device to be monitored, captured, and

recorded for protocol analysis. The card is compatible with the Summit T516 and Summit T54 and supports data rates

of 2.5 GT/s, 5.0 GT/s, 8.0 GT/s, 16.0 GT/s and 32 GT/s. The interposer supports side band signals such as PERST#,

WAKE#, CLKREQ# and SMBus (SMBCLK, SMBDAT). The interposer can be used with Single x4 Port or Dual x2 Ports.

It also supports U.2 and U.3 standards. It can be used also with Summit T4 and Summit M5x analyzers using a

conversion cable.

When the U.2/U.3 12 inch Interposer is upgraded with CrossSync PHY technology it will provide enhanced power

management and link training equalization debugging capability, enabling users to see and correlate both the physical

and protocol layers in a unified time aligned view. No other solution gives this type of insight into link behavior.

PCI Express 5.0 U.2/U.3 12 Inch Interposer

1

2