EVK-NORA-B1 - User guide

UBX-20030319 - R05 Contents Page 3 of 32

C1-Public

Contents

Document information .............................................................................................................................2

Contents .......................................................................................................................................................3

1Product description............................................................................................................................4

1.1 Key features ................................................................................................................................................. 4

1.2 Items included in kit....................................................................................................................................5

1.2.1 EVK-NORA-B100 kit contents .........................................................................................................5

1.2.2 EVK-NORA-B106 kit contents .........................................................................................................5

1.3Development tools ......................................................................................................................................5

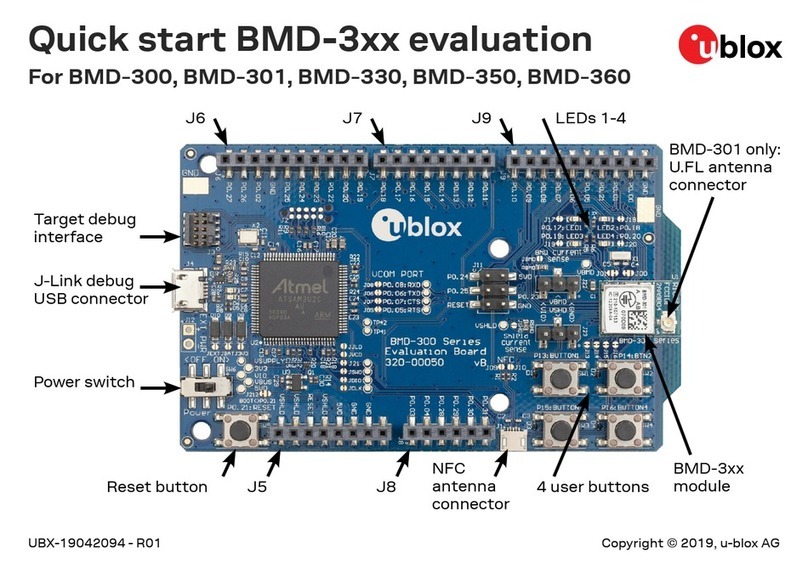

2Hardware description.........................................................................................................................6

2.1 Power .............................................................................................................................................................6

2.1.1 Powering the board ............................................................................................................................6

2.1.2 USB peripheral power.........................................................................................................................6

2.2 Reset..............................................................................................................................................................7

2.3 Buttons..........................................................................................................................................................8

2.4 LEDs...............................................................................................................................................................9

2.5 Serial communication ..............................................................................................................................10

2.6 32.768 kHz low frequency clock.............................................................................................................11

2.7 NFC connector...........................................................................................................................................12

2.8 Current sensing headers .........................................................................................................................13

2.9 Debug indicators .......................................................................................................................................13

2.10External SEGGER J-Link™ debug interface ........................................................................................14

2.11QSPI .............................................................................................................................................................15

2.12GPIO jumpers .............................................................................................................................................15

2.13Header pin-out ...........................................................................................................................................16

3SEGGER Embedded Studio and NORA-B1 CPU cores........................................................... 20

4Application development............................................................................................................... 21

4.1 Install nRF Connect for Desktop............................................................................................................21

4.1.1 Install nRF Connect SDK.................................................................................................................22

4.1.2 Board support package ...................................................................................................................22

4.1.3 Prepare working copies of the sample applications..................................................................22

4.1.4 Prepare EVK.......................................................................................................................................23

4.1.5 Build and load network core............................................................................................................24

4.1.6 Build and load application core ......................................................................................................26

4.2 Test the application..................................................................................................................................27

Appendix .................................................................................................................................................... 30

AGlossary .............................................................................................................................................. 30

Related documentation......................................................................................................................... 31

Revision history ....................................................................................................................................... 31

Contact....................................................................................................................................................... 32