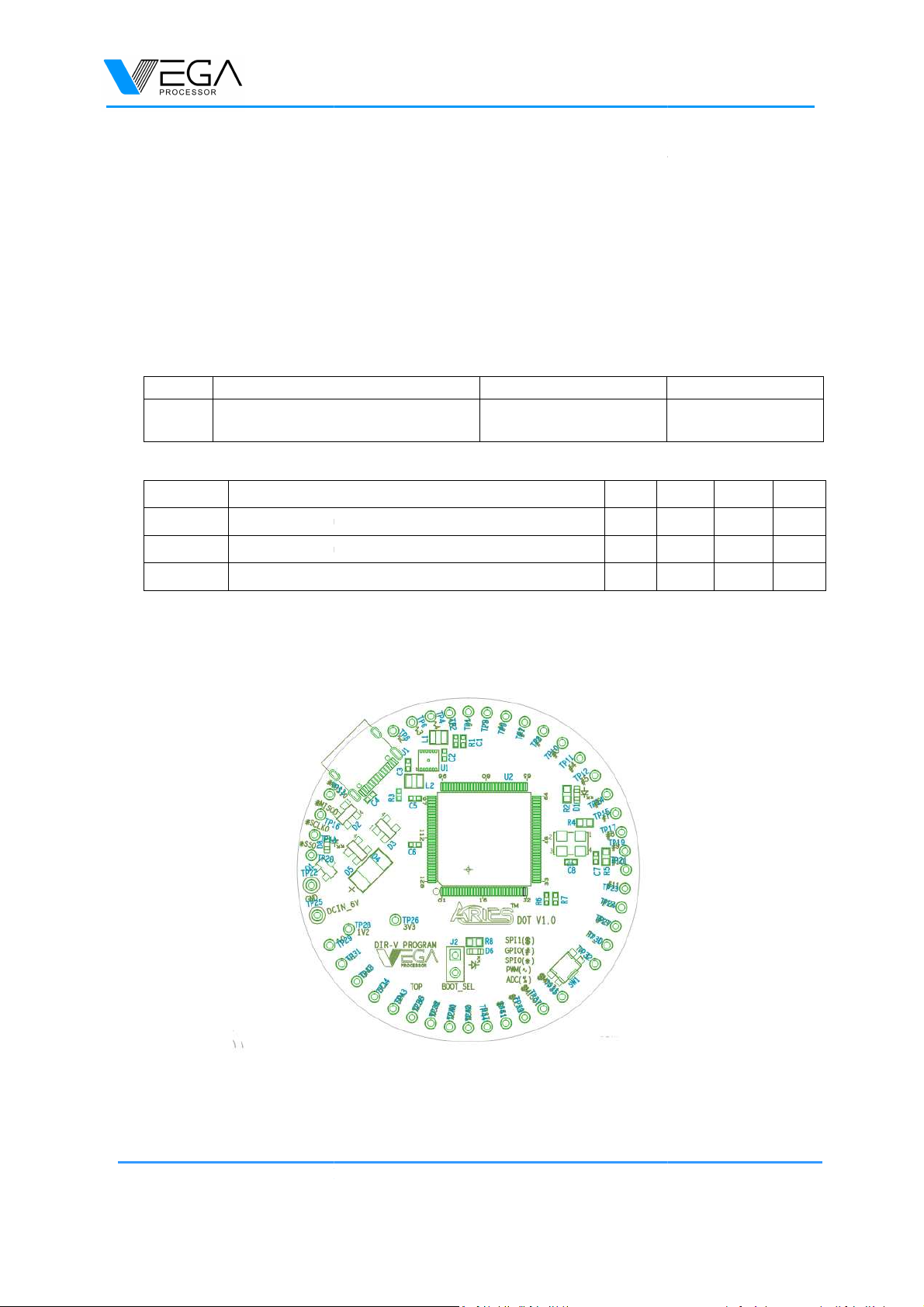

ARIES DOT V1.0

© August, 2023 Centre for Development of Advanced Computing (C-DAC) Page | 5/

Ref. Description Ref. Description

J1 USB C Connector U2 THEJAS32 SoC

J2 Boot Select Header U1 Regulator

SW1 Reset Button U4 100 MHz Oscillator

D1 LED D6 Processor HeartBeat LED

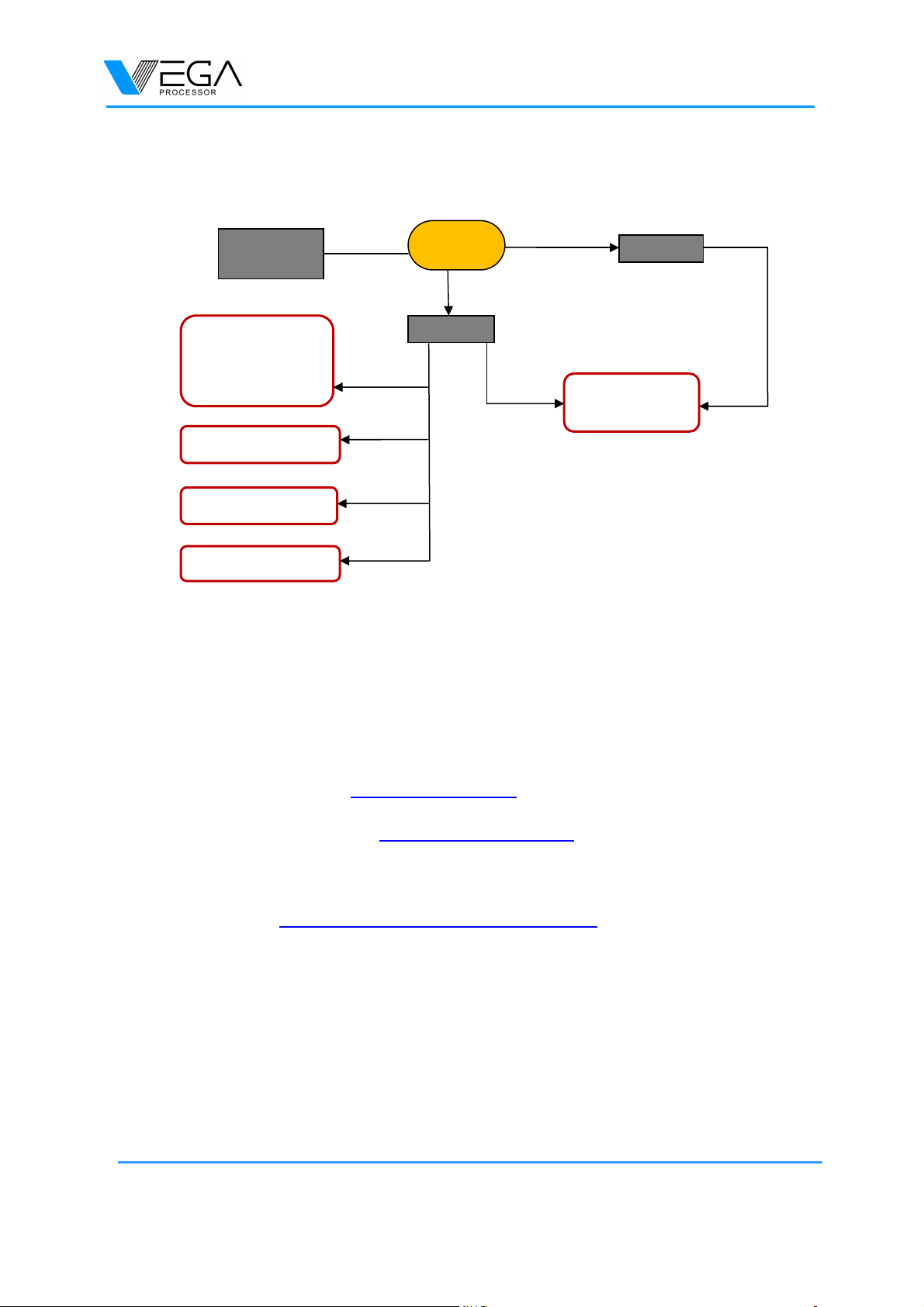

3.2 Processor

The main controller is THEAJS32 SoC which operates at a frequenc of 100MHz. It includes VEGA ET1031

Microprocessor, 256KB internal SRAM, Three UARTs, Four SPIs, Three TIMERs, Eight PWMs, Three I2C

interface, 32 GPIOs. Most of its pins are connected to the external headers, however some are reserved for

internal communication.

3.3 THEJAS32 pinout

Pin # Pin Name Pin Description

Ground reference for IO pins.

Positive suppl for IO pins. Connect to 3.3V suppl .

SPI 3 Master Out Slave In.

Positive suppl for logic. Connect to 1.2V suppl .

Ground reference for logic.

SPI 3 Master In Slave Out.

Ground reference for IO pins.

pins. Connect to 3.3V suppl .

Positive suppl for logic. Connect to 1.2V suppl .

Ground reference for logic.

Connect to GND through a 1K resistor.

JTAG TDO. Left unconnected.

JTAG TMS. Connect to GND through a 1K resistor.

JTAG TDI. Connect to GND through a 1K resistor.

Ground reference for IO pins.

25 PVDDIO19 Positive suppl for IO pins. Connect to 3.3V suppl .

Positive suppl for logic. Connect to 1.2V suppl .

Ground reference for logic.

JTAG TCK. Connect to GND through a 1K resistor

JTAG TRST. Connect to GND through a 1K resistor

Connect to GND through a 1K resistor.