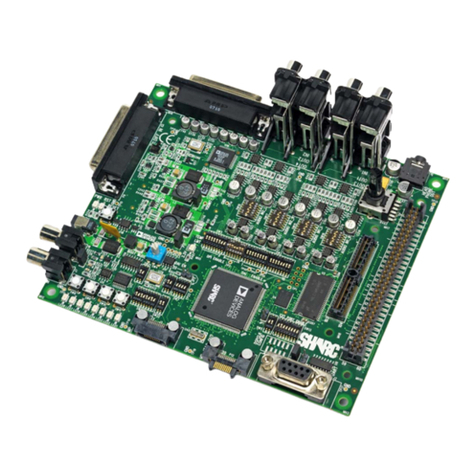

Analog Devices SHARC ADSP-21065L User manual

Other Analog Devices Computer Hardware manuals

Analog Devices

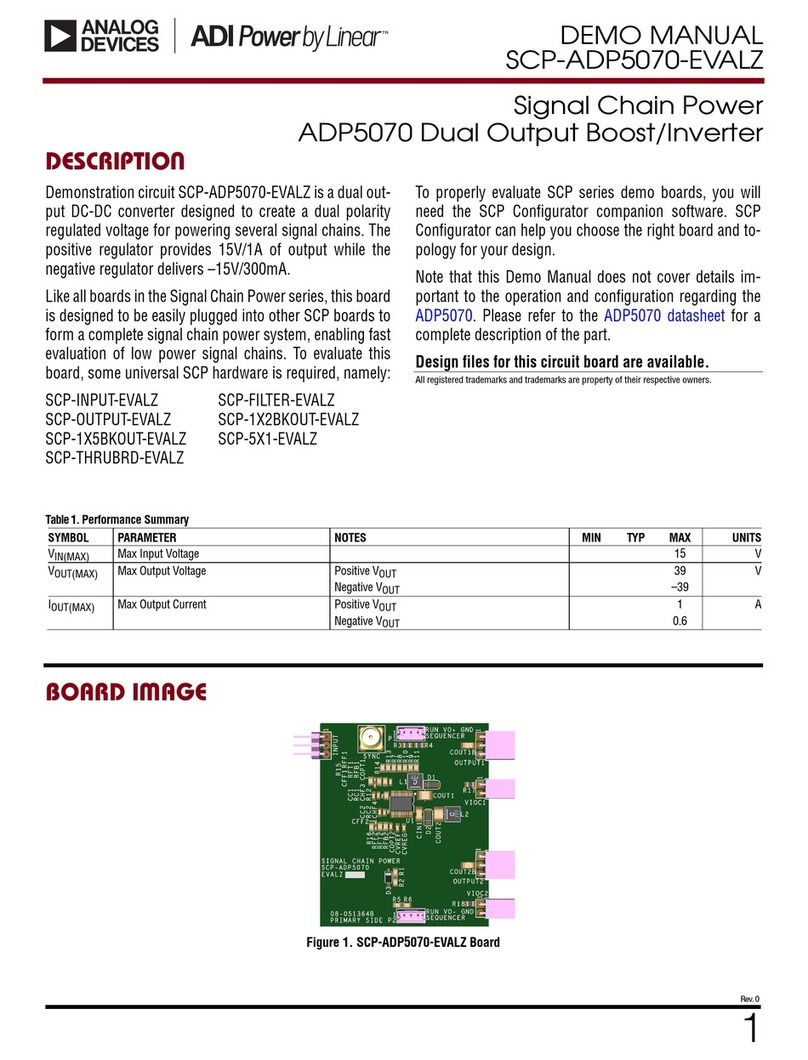

Analog Devices Linear ADP5070 Quick setup guide

Analog Devices

Analog Devices EZ-Extender PWM 180-Pin User manual

Analog Devices

Analog Devices EZ-KIT LITE ADSP-2191 User manual

Analog Devices

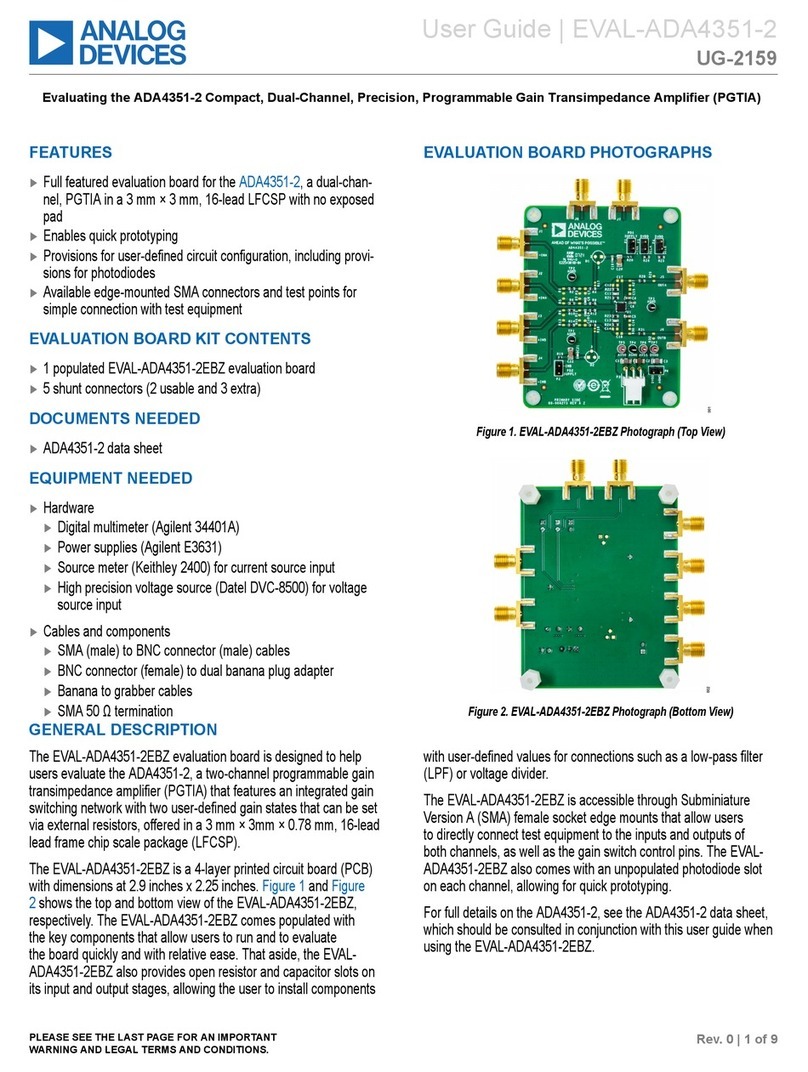

Analog Devices EVAL-ADA4351-2 User manual

Analog Devices

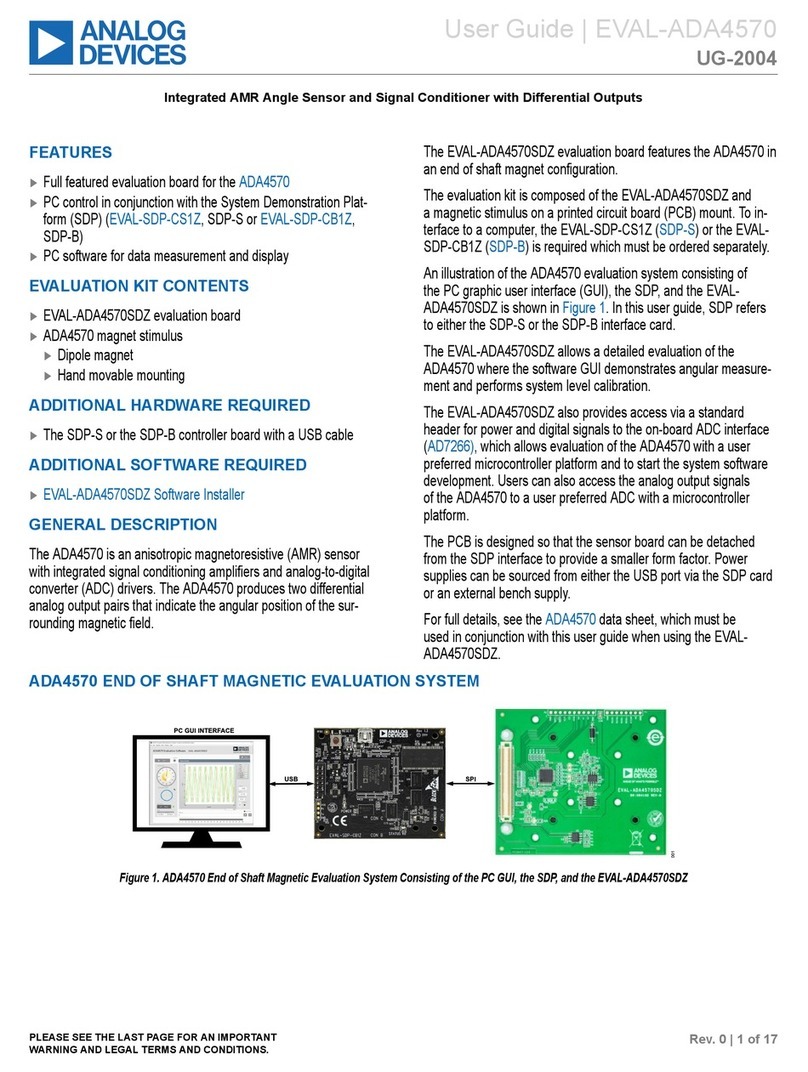

Analog Devices EVAL-ADA4570SDZ User manual

Analog Devices

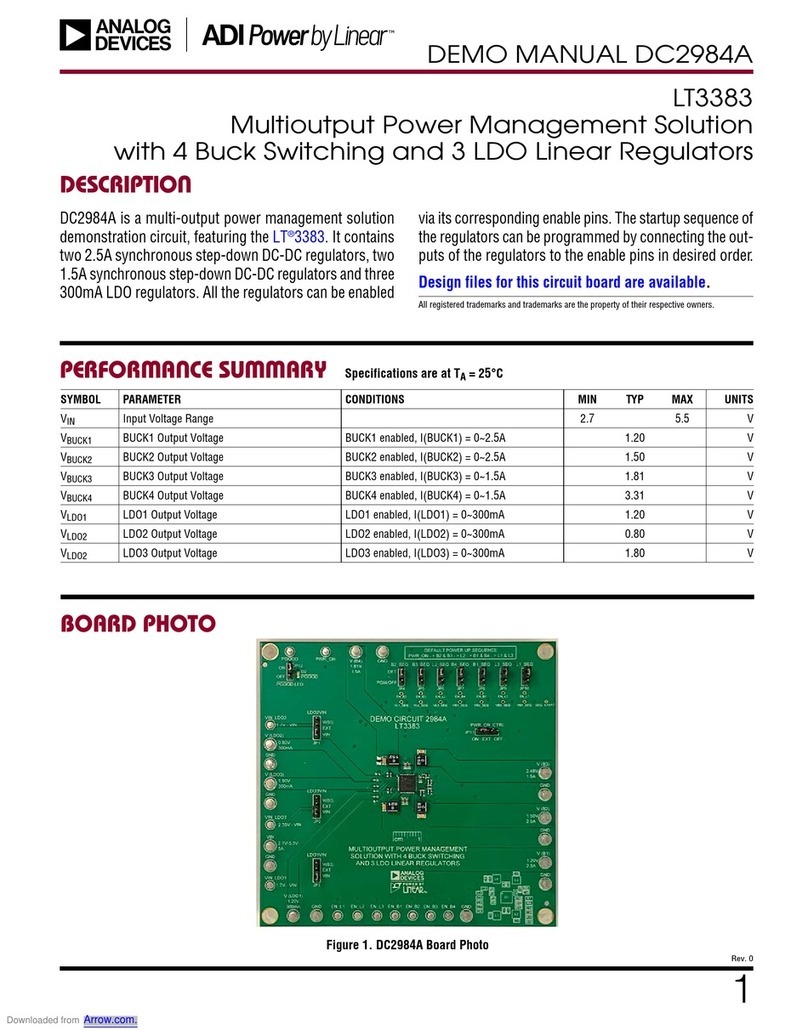

Analog Devices Linear LT3383 Quick setup guide

Analog Devices

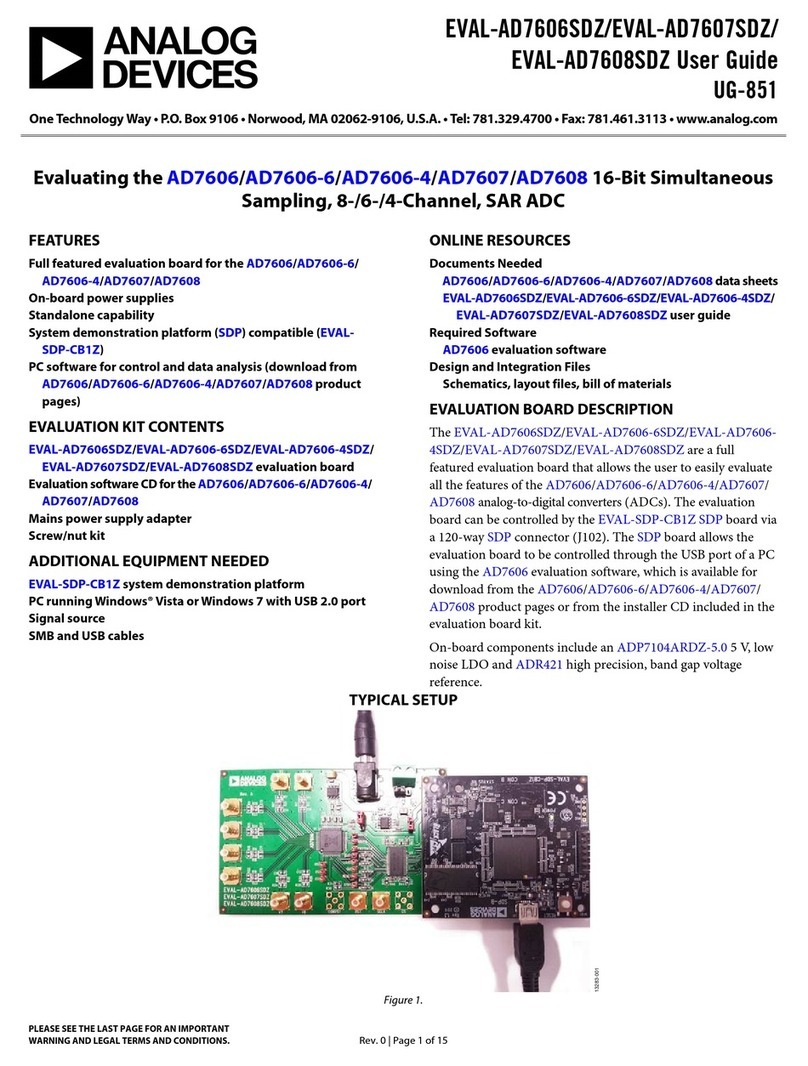

Analog Devices EVAL-AD7606SDZ User manual

Analog Devices

Analog Devices LINEAR DC2672A-A Quick setup guide

Analog Devices

Analog Devices EVAL-ADAU1772Z User manual

Analog Devices

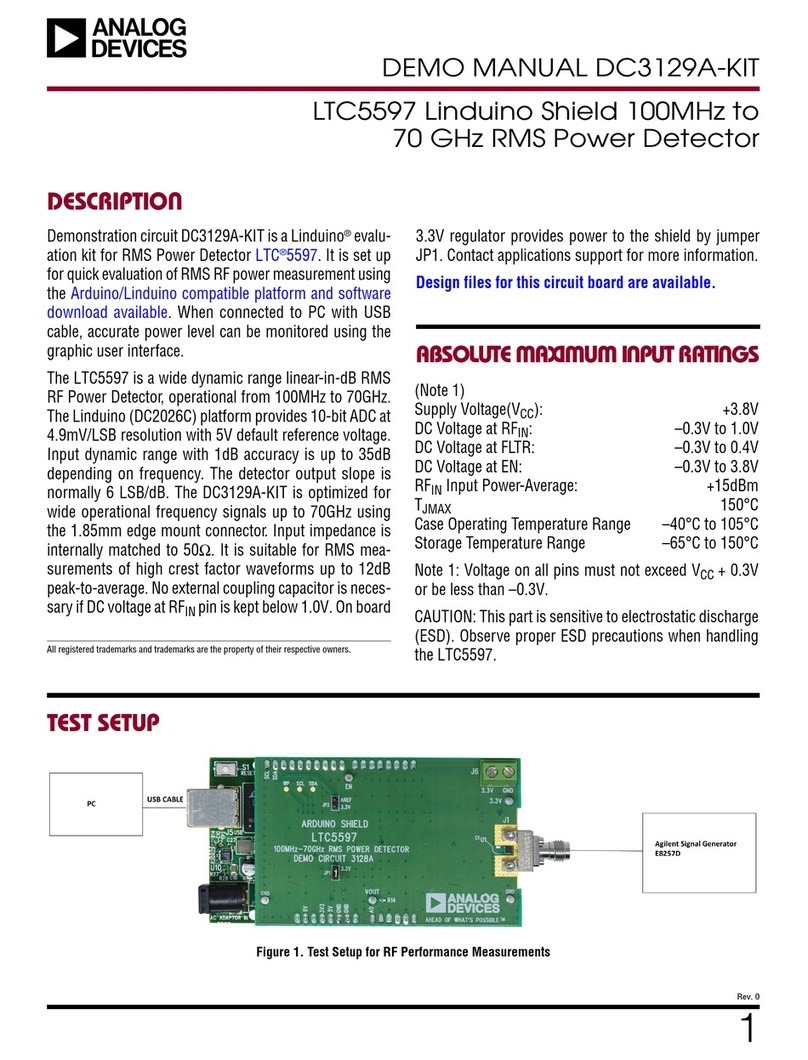

Analog Devices LTC5597 User manual

Analog Devices

Analog Devices ADAU1961 User manual

Analog Devices

Analog Devices ADSP-BF53x Blackfin Service manual

Analog Devices

Analog Devices ADSP-CM419F User manual

Analog Devices

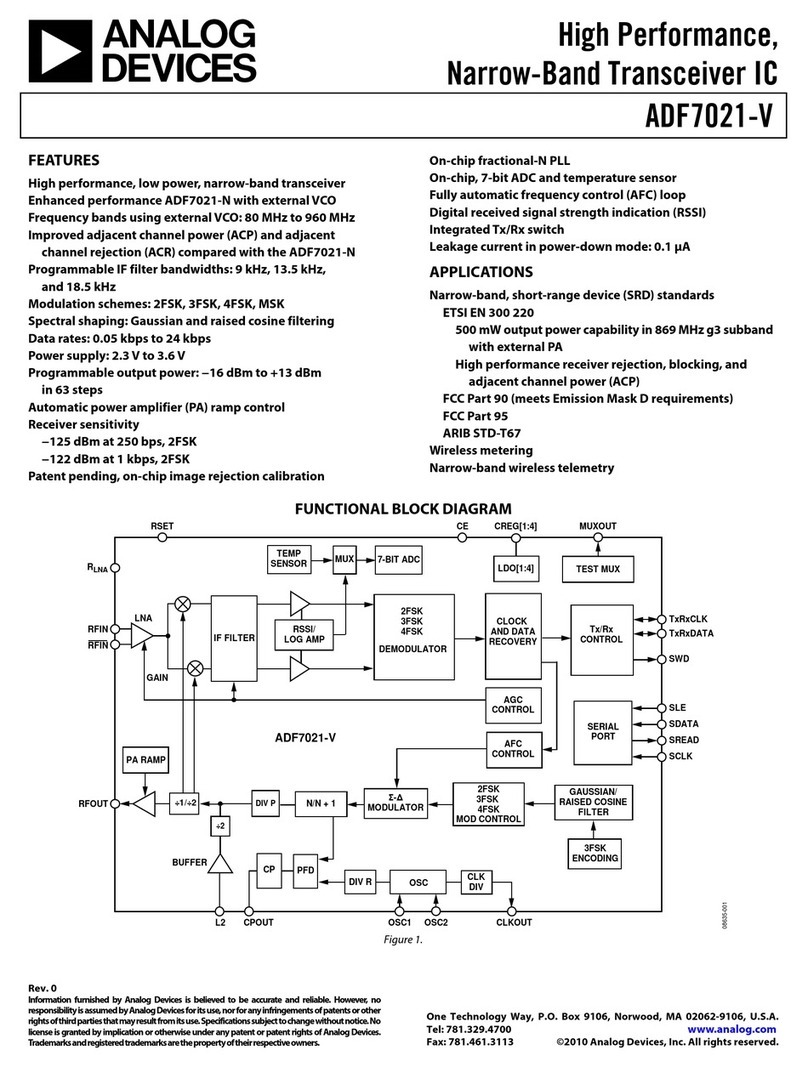

Analog Devices ADF7021-V User manual

Analog Devices

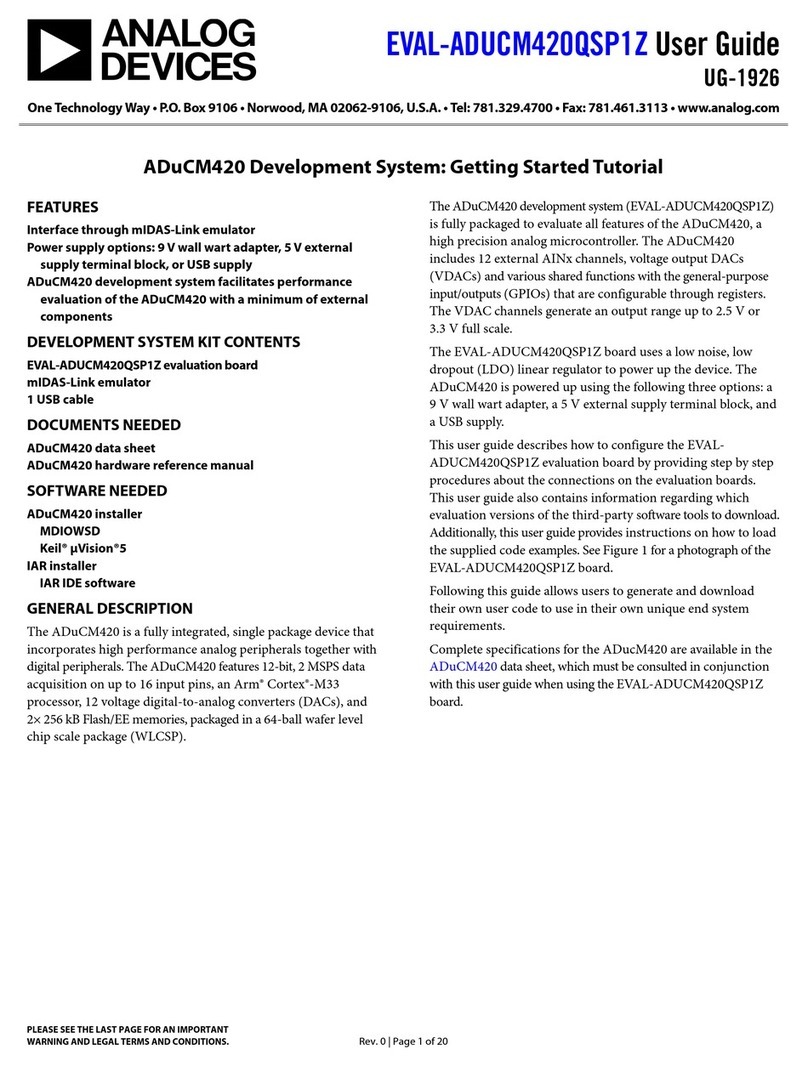

Analog Devices EVAL-ADuCM420QSP1Z User manual

Analog Devices

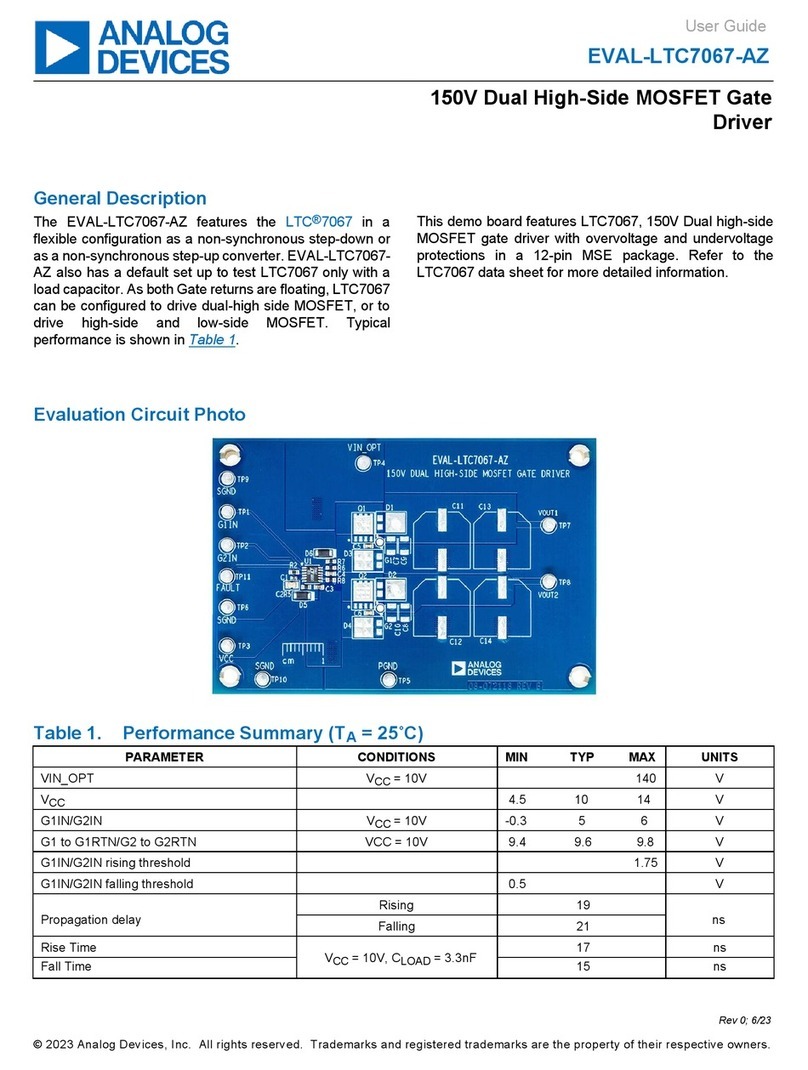

Analog Devices EVAL-LTC7067-AZ User manual

Analog Devices

Analog Devices EVAL-ADN4650EB1Z User manual

Analog Devices

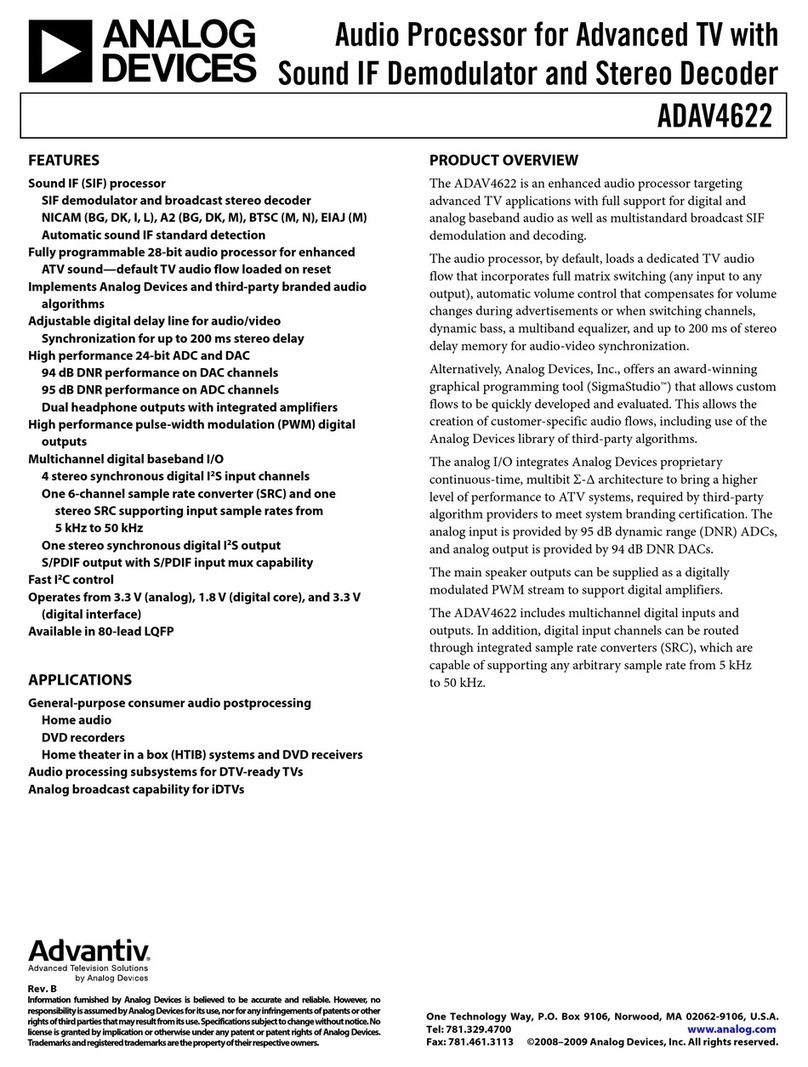

Analog Devices ADAV4622 User manual

Analog Devices

Analog Devices EVAL-ADF4152HVEB1Z User manual

Analog Devices

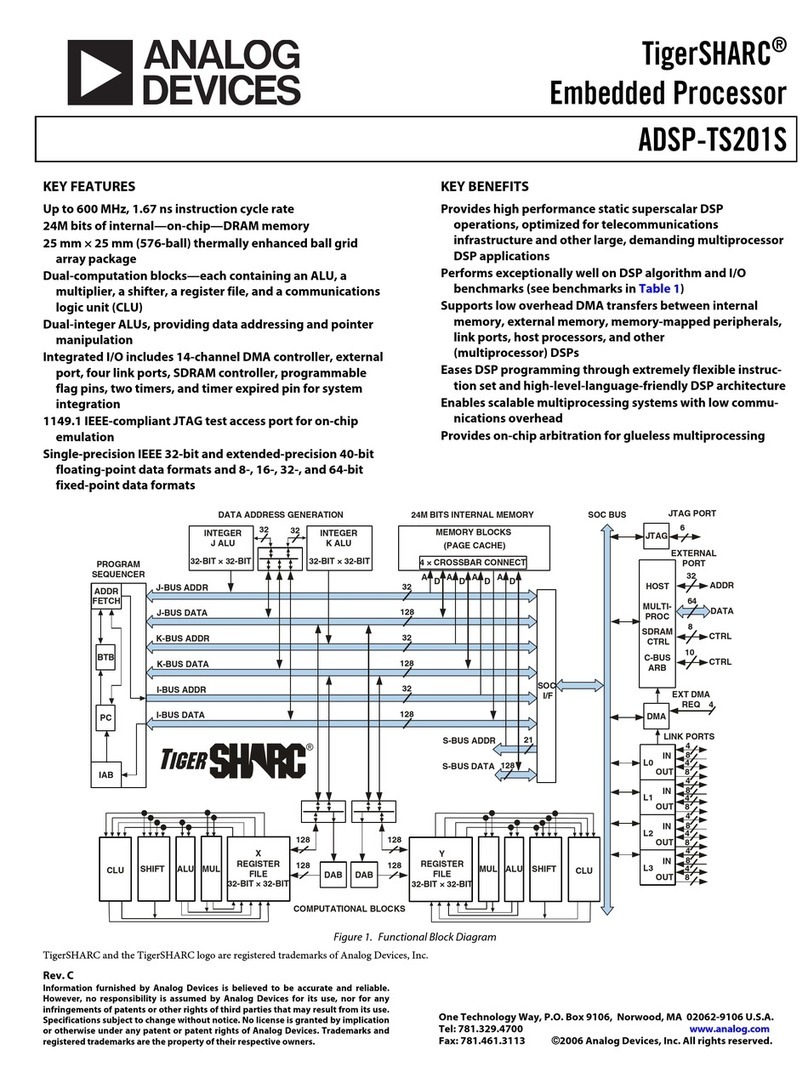

Analog Devices TigerSHARC ADSP-TS201S User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual