ADT7473/ADT7473-1

Rev. C | Page 2 of 72

TABLE OF CONTENTS

Features .............................................................................................. 1

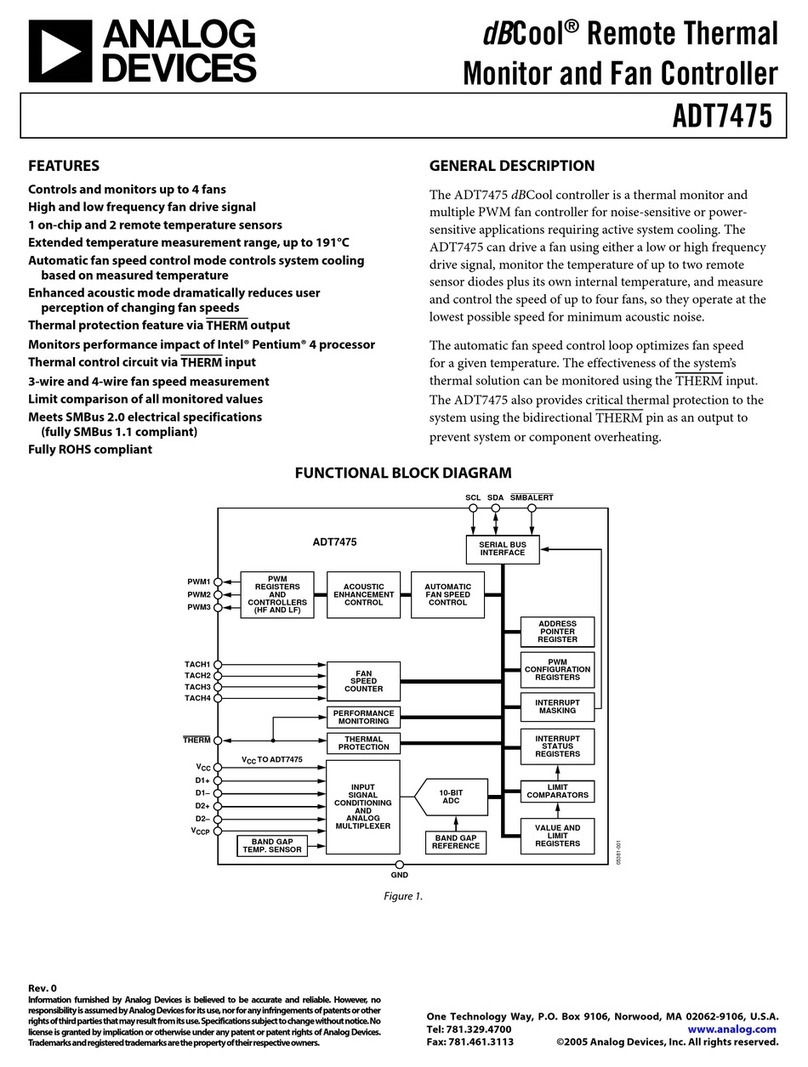

General Description......................................................................... 1

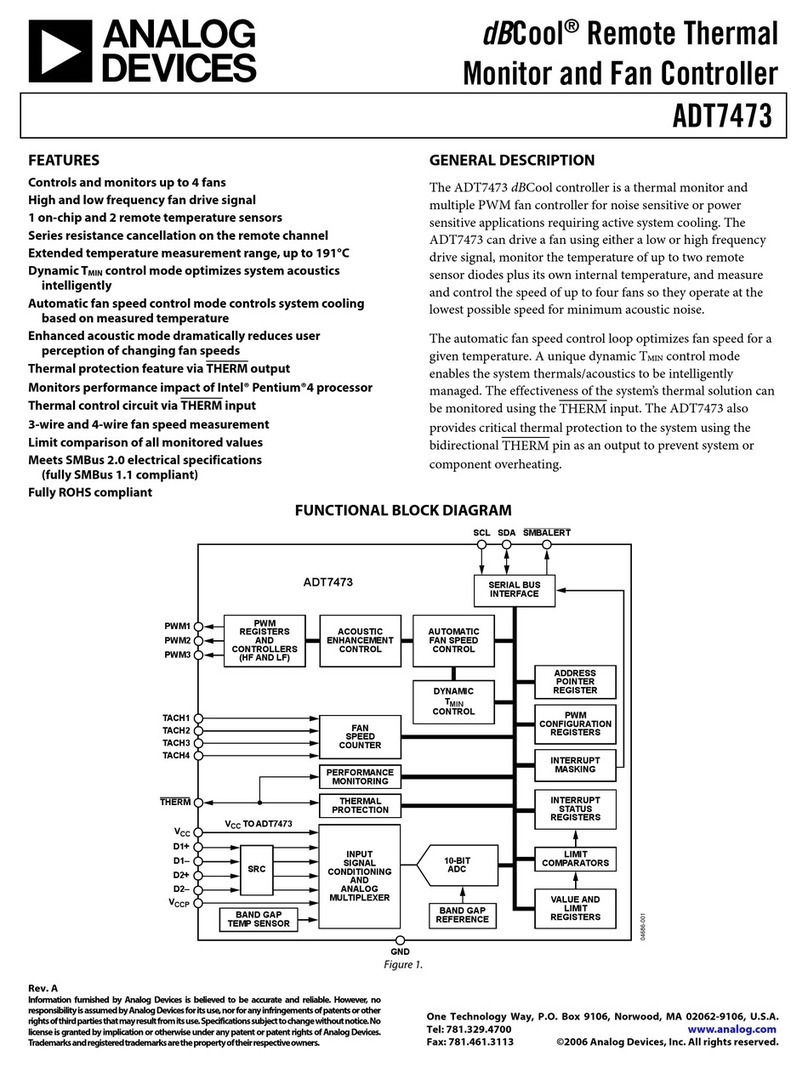

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Diagram ........................................................................... 4

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution.................................................................................. 5

Pin Configurations and Function Descriptions ........................... 6

Typical Performance Characteristics ............................................. 7

Product Description......................................................................... 9

Comparison Between ADT7467 and ADT7473/ADT7473-1 9

How to Set the Functionality of Pin 9........................................ 9

Recommended Implementation................................................. 9

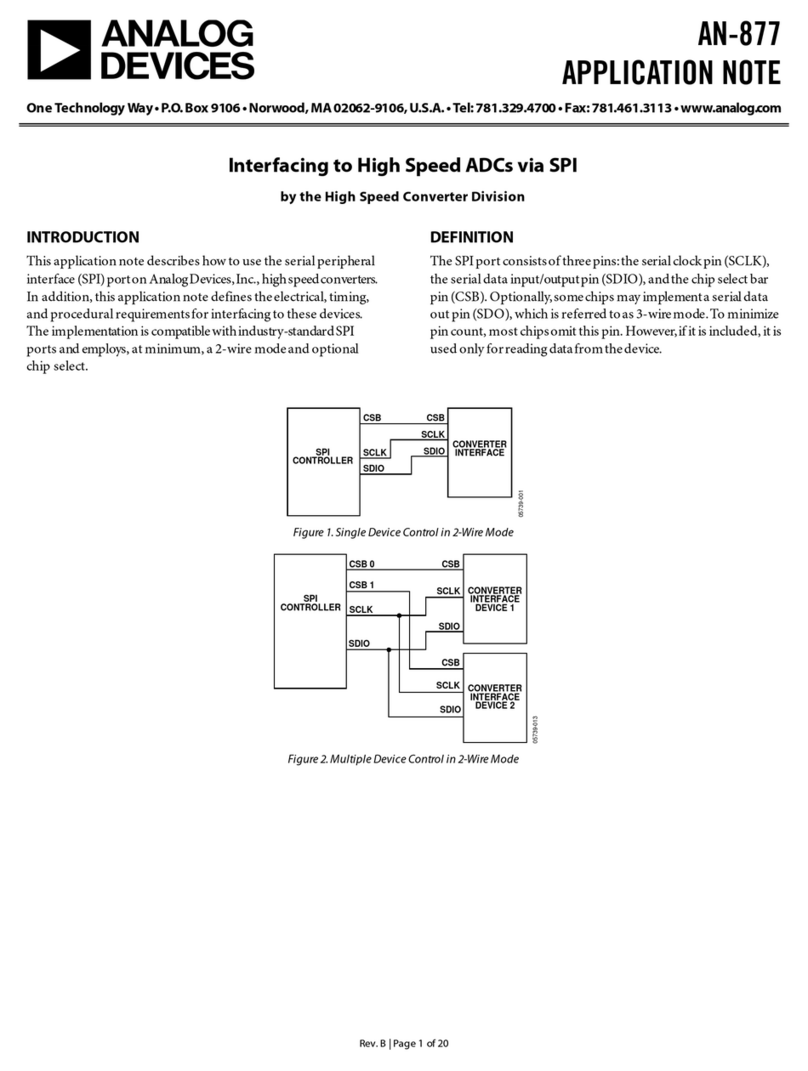

Serial Bus Interface..................................................................... 10

Write Operations ........................................................................ 12

Read Operations ......................................................................... 13

SMBus Timeout .......................................................................... 13

Voltage Measurement Input...................................................... 13

Analog-to-Digital Converter .................................................... 13

Input Circuitry ............................................................................ 13

Voltage Measurement Registers................................................ 13

VCCP Limit Registers ................................................................... 13

Additional ADC Functions for Voltage Measurements ........ 14

Temperature Measurement Method ........................................ 15

Series Resistance Cancellation.................................................. 17

Factors Affecting Diode Accuracy ........................................... 17

Additional ADC Functions for Temperature Measurement 19

Limits, Status Registers, and Interrupts....................................... 20

Limit Values ................................................................................ 20

Interrupt Status Registers .......................................................... 21

THERM Timer ........................................................................... 23

Fan Drive Using PWM Control ............................................... 25

Fan Presence Detect................................................................... 30

Sleep States .................................................................................. 30

XNOR Tree Test Mode .............................................................. 30

Power-On Default ...................................................................... 31

Programming the Automatic Fan Speed Control Loop ............ 32

Automatic Fan Control Overview............................................ 32

Step 1: Hardware Configuration .............................................. 33

Step 2: Configuring the Mux .................................................... 35

Step 3: TMIN Settings for Thermal Calibration Channels ...... 37

Step 4: PWMMIN for Each PWM (Fan) Output ...................... 38

Step 5: PWMMAX for PWM (Fan) Outputs.............................. 38

Step 6: TRANGE for Temperature Channels................................ 39

Step 7: TTHERM for Temperature Channels ............................... 42

Step 8: THYST for Temperature Channels.................................. 43

Dynamic TMIN Control Mode ................................................... 44

Step 9: Operating Points for Temperature Channels............. 46

Step 10: High and Low Limits for Temperature Channels ... 47

Step 11: Monitoring THERM ................................................... 49

Enhancing System Acoustics .................................................... 50

Step 12: Ramp Rate for Acoustic Enhancement..................... 52

Register Tables ................................................................................ 54

Outline Dimensions ....................................................................... 72

Ordering Guide .......................................................................... 72

REVISION HISTORY

8/07—Rev. B to Rev. C

Changes to Interrupt Status Register 2 (0x42) section .............. 21

Changes to High Frequency Mode PWM Drive section .......... 29

Changes to Table 20........................................................................ 54

Changes to Table 51........................................................................ 67

Changes to Table 61........................................................................ 71

6/07—Rev. A to Rev. B

Added ADT7473-1.............................................................Universal

2/06—Rev. 0 to Rev. A.

Changes to Table 1............................................................................ 4

Change to Table 3 ..............................................................................6

Changes to Comparisons Between the ADT7467

and ADT7476 section .................................................................... 10

Changes to SMBALERT Interrupt Behavior Section ................ 21

Changes to Interrupt Mask Register 1 (0x74) Section............... 22

Changes to Fan Drive Using PWM Control ............................... 26

Changes to Reading Fan Speed from the ADT7473.................. 28

Changes to Ordering Guide.......................................................... 76

6/05—Revision 0: Initial Version