I.

II.

III.

IV.

v.

VI.

TABLE

OF

CONTENTS

INTRODUCTION.

• •• • ••• •• •• • •• •• • •• •• •• •• • ••. • • •

I.

1

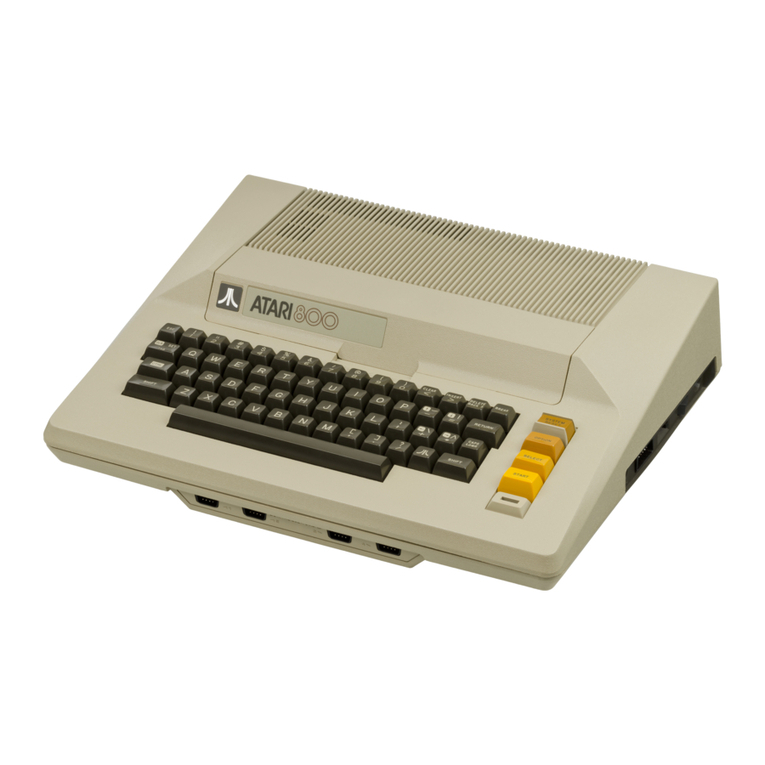

DESCRIPTION

OF

HARDWARE

••••••••••••••••••••••

II.1

A.

ANTIC

and

CTIA

•••••••••

••••••••••••••

•••

II.1

B.

POKEY

••••••••••••••••••••••••••••••

•••••

11.23

C.

SERIAL

PORT

•••••••••••••••••••••••••••••

II.25

D.

INTERRUPT

SYSTEM

••••••••••••••••••••••••

II.28

E.

CONTROLLERS

•••••••••••••••••••••••••••••

II.30

HARDWARE

REGISTERS

••••••••••••••••••••••••••

III

.1

A.

PAL••••••••••••••••••••••••••••••••••••III.l

B.

INTERRUPT

CONTROL

••••••••••••••••••••••

III.1

C.

TV

LINE

CONTROL

••••••••••••••••••••••••

III.3

D.

GRAPHICS

CONTROL

••••••••••••••

•••••••••

III.4

E.

PLAYERS

AND

MISSILES

•••••••••••••••••••

III.9

F.

AUDIO

•

•••••••••••••••••••••••••••••••••

I I

I.

12

G.

KEYBOARD

and

SPEAKER

•••••••••••••••••••

III.15

H.

SERIAL

PORT••••••••••••••••••••••••••••III.17

I.

CONTROLLER

PORTS

•••••••••••••••••••••••

III.19

SAMPLE

DISPLAY

PROGRAM

•••••••••••••••••••••••

IV.1

HARDWARE

REGISTER

LISTS

•••••••••••••••••••••••

V.1

A.

ADDRESS

ORDER.

•••••••••••••••••••••••••••V.1

B.

ALPHABETICAL

ORDER

•••••••••••••••••••••••

V.S

FIGURES

•

•••••••••••••••••••••••••••••••••••••

VI.

1

A.

11EMORY

MAP

•

•••••••••••••••••••••••••••••

VI.

1

B.

NTSC

and

PAL

DISPLAY

••••••••••••••••••••

VI.2

C.

SCHEMATICS

•

••••••••••••••••••••••••

••••

•

VI.

3

APPENDIX

A:

APPENDIX

B:

APPENDIX

C

USE

OF

PLAYER/MISSILE

GRAPHICS

WITH

BASIC

MIXING GRAPHICS

MODES

PINOUTS

ii