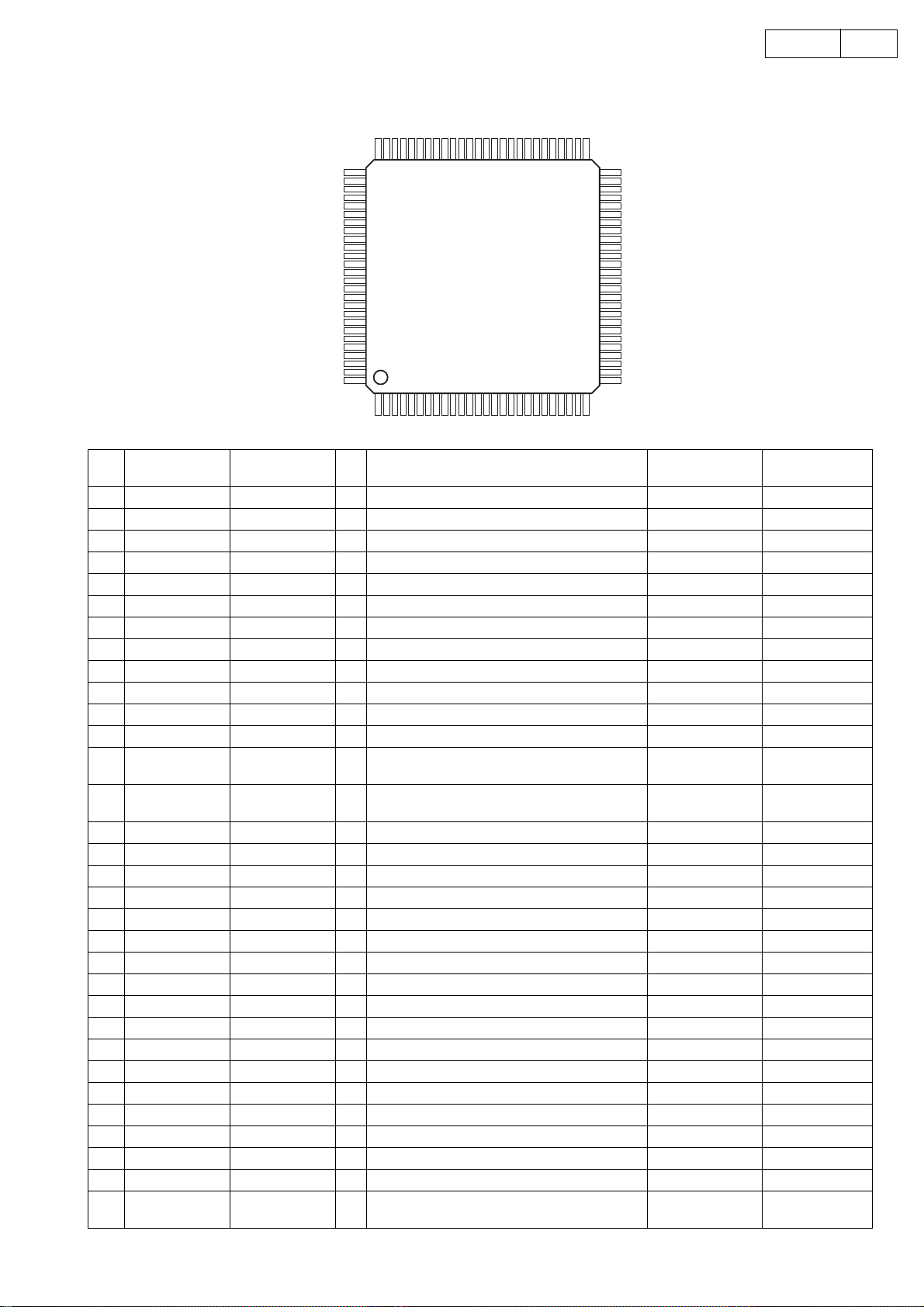

10

10UD-M31

33 AVSS AVSS - A/D,D/A converter GND position OTHER -

34 P130/ANO0 LINE1 O LINE OUT Control signal output1 OTHER L

35 P131/ANO1 LINE2 O LINE OUT Control signal output2 OTHER L

36 AVref1 Avref1 - D/A converter reference voltage input OTHER -

37 P70/RxD2/SI2 SQOUT I Sub Q code data input CD L

38 P71/TxD2/SO2 COIN O CD-DSP serial communication data output CD L

39 P72/ASCK2/

SCK2

CQCK O CD-DSP serial communication clock output CD L

40 P20/RxD1/SI1 NC I Pull up RECIEVER -

41 P21/TxD1/SO1 FLDT O DATA BUS for FL driver, Data output RECIEVER L

42 P22/ACSK1/

SCK1

FLCLK O DATA BUS for FL driver, Clock output RECIEVER L

43 P23/PCL NC I Pull up RECIEVER -

44 P24/BUZ /RDSRST O RDS IC reset output RECIEVER -

45 P25/SI0/SDA0 DB RXD I DATA BUS for DENON BUS Data input RECIEVER -

46 P26/SO0 DB TXD O DATA BUS for DEON BUS Data output RECIEVER L

47 P27/SCK0/SCL0 DB CLK O DENON BUS Clock output RECIEVER L

48 P80/A0 /SD I FM/AM Tuning signal input, Tuned:Low RECIEVER -

49 P81/AÇP /ST INC I FM stereo demodulation detect input, Ste-

reo:Low

RECIEVER -

50 P82/A2 /TMUTE O Tuner mute output, mute:Low RECIEVER L

51 P83/A3 AUTO/MONO O FM AUTO/MONO switching, MONO:High RECIEVER L

52 P84/A4 USA I Initial setting input RECIEVER -

53 P85/A5 EURO I Initial setting input RECIEVER -

54 P86/A6 FREQ I Initial setting input RECIEVER -

55 P87/A7 RDS I Initial setting input RECIEVER -

56 P40/AD0 SL+ O SLIDE kick Forward CD L

57 P41/AD1 SL- O SLIDE kick Reverse CD L

58 P42/AD2 CD/!RW O CD, CD-RW gain switching CD L

59 P43/AD3 SERACH O SEARCH control CD L

60 P44/AD4 NC O OPEN CD L

61 P45/AD5 NC O OPEN CD L

62 P46/AD6 LED POWER G O POWER/STANDBY Green LED out-

put,Light:High

63 P47/AD7 LED POWER R O POWER/STANDBY Red LED output,Light:High

64 P50/A8 NC I Pull up CD -

65 P51/A9 NC I Pull up CD -

66 P52/A10 CLSW I LOADER CLOSE SW input CD -

67 P53/A11 OPSW I LOADER OPEN SW input CD -

68 P54/A12 NC I Pull up CD -

69 P55/A13 NC I Pull up CD -

70 P56/A14 NC I Pull up CD -

71 P57/A15 O Not used :NC OTHER L

72 VSS VSS - GND potential OTHER -

73 P60/A16 BLK O FLD ON/OFF control port, L= black out FLD

74 P61/A17 DATXD O DATA BUS(for VOL,PLL,RDS IC, EEPROM)

Data output

RECIEVER L

75 P62/A18 DACLK O DATA BUS(for VOL,PLL,RDS IC, EEPROM)

Clock output

RECIEVER L

76 P63/A19 DACE O DATA BUS(for VOL,PLL,RDS IC) Chip enable

output

RECIEVER L

77 P64/RD DRP_RST O CD-DSP reset output, output, reset:High CD L

78 P65/WR O Not used :NC OTHER L

79 P66/WAIT PWBCHK I Start PWB check mode OTHER -

Pin

No. Port Symbol I/O Function RECIEVER or CD outputs of

standby&Defoult