Epiq Solutions Sidekiq Z2 User manual

Sidekiq Z2 and Matchstiq Z3u FPGA

Development Manual

Version 3.16.2

Updated 03/10/22

Disclaimer

Epiq Solutions is disclosing this document (“Documentation”) as a general guideline or

development. Epiq Solutions expressly disclaims any liability arising out o your use o the

Documentation. Epiq Solutions reserves the right, at its sole discretion, to change the

Documentation without notice at any time. Epiq Solutions assumes no obligation to correct

any errors contained in the Documentation, or to advise you o any corrections or updates.

Epiq Solutions expressly disclaims any liability in connection with technical support or

assistance that may be provided to you in connection with the In ormation.

THE DOCUMENTATION IS DISCLOSED TO YOU “AS IS” WITH NO WARRANTY OF ANY

KIND. EPIQ SOLUTIONS MAKES NO OTHER WARRANTIES, WHETHER EXPRESSED,

IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR

NONINFRINGEMENT OF THIRD PARTY RIGHTS. IN NO EVENT WILL EPIQ SOLUTIONS

BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR

INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING

FROM YOUR USE OF THE DOCUMENTATION.

All material in this document is Copyrighted by Epiq Solutions 2022. All trademarks are

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

2

property o their respective owners.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

3

Revision Histor

Date Revision Description

06/06/2018 3.9.0 Initial release.

09/10/2018 3.10.0 FPGA builds are now built as part o the top level project Linux build

process. Add basic Tx capability.

12/12/2018 3.10.0 Document updates only. Update to section 8.2.1, added instructions on

how to obtain the actual schematic in Vivado or Figure 5, and added in o

about user_app reg x8708. Update build instructions.

04/25/2019 3.12.0 Add requency hopping control logic. Upgrade to Vivado 2018.2.

Add iq swap mode.

09/09/2019 3.12.0 Doc update only, update in o about pga programming.

01/14/2021 3.14.1 Fix FIFO ull write bug which resulted in the Rx header and sample data

to be scrambled in certain circumstances.

Fix bug where Rx would enter packed mode when not requested which

resulted in the timestamp being o by 338 counts and the data scrambled

as i it were in packed mode.

Fix or starting/stopping streaming on a 1PPS edge.

04/12/2021 3.15.1 Z3u: Add GPS_CONTROL_MASK read only register.

Z3u: Add gps_pps mux control.

All: Fix missing timestamp reset related to clock crossing synchronization

on the register inter ace.

All: Add register reset capability.

All: Add BASELINE_VCS_STATUS register.

All: Add rc_sel_ or_tx to be used in Tx timestamp mode.

10/29/2021 3.15.1

Updated

10/29/21

Documentation update only relating to pga programming and packed

mode not being available on the Z plat orms.

03/10/2022 3.16.2 Z3u: Add board_id to the FPGA_REG_VERSION register or Zu3 RevD.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

4

Table of Contents

1 About this Document..........................................................................................................................8

2 Legal Considerations.........................................................................................................................8

3 Proper Care and Handling.................................................................................................................8

4 Introduction........................................................................................................................................ 9

5 Re erences...................................................................................................................................... 10

6 Terms and De initions......................................................................................................................10

7 FPGA Re erence Design..................................................................................................................12

7.1 Overview.................................................................................................................................. 12

7.2 Top Level..................................................................................................................................13

7.3 user_app.................................................................................................................................. 14

7.3.1 user_app Signals.............................................................................................................. 15

7.3.2 Rx Path Inputs to user_app..............................................................................................16

7.3.3 Outputs rom user_app.....................................................................................................17

7.3.4 user_app Tx Inter ace.......................................................................................................18

7.3.5 user_reg_i ........................................................................................................................ 18

7.4 reg_i / user_reg_i ...................................................................................................................19

7.5 iio_data_i ................................................................................................................................. 20

7.6 timestamp_block......................................................................................................................20

7.7 gpio/uart................................................................................................................................... 21

7.8 system_wrapper.......................................................................................................................22

7.8.1 Sidekiq Z2 system_wrapper..............................................................................................22

7.8.2 Matchstiq Z3u system_wrapper........................................................................................22

8 Building and Debugging................................................................................................................... 26

8.1 Building a user_app..................................................................................................................26

8.1.1 Sidekiq Z2 Re erence Design...........................................................................................26

8.1.2 Matchstiq Z3u Re erence Design......................................................................................26

8.1.3 Custom user_apps............................................................................................................27

8.2 Building the project and bitstream............................................................................................27

8.3 Build with Linux........................................................................................................................ 28

8.3.1 Building Sidekiq Z2...........................................................................................................28

8.3.2 Building Matchstiq Z3u......................................................................................................28

8.4 Build with Windows..................................................................................................................29

8.5 Programming............................................................................................................................ 29

8.5.1 Programming the Sidekiq Z2 FPGA..................................................................................29

8.5.2 Programming the Matchstiq Z3u FPGA............................................................................29

8.6 Testing the Bitstream................................................................................................................ 29

8.7 Using JTAG or Debug.............................................................................................................29

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

5

Table of Figures

Figure 1: Sidekiq Z2 Simpli ied Block Diagram....................................................................................13

Figure 2: User App Block Diagram.......................................................................................................14

Figure 3: Sample Timing Diagram........................................................................................................17

Figure 4: Sample User App to IIO Diagram..........................................................................................18

Figure 5: Sidekiq Z2 Zynq Processing System....................................................................................25

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

6

Table of Tables

Table 1: Terms and De initions.............................................................................................................11

Table 2: Rx Control Register................................................................................................................15

Table 3: User Registers........................................................................................................................19

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

1 About this Document

This document provides the necessary details or developing FPGA applications on the SidekiqTM Z2

SDR or the Matchstiq Z3u SDR developed by Epiq Solutions [1]. It is provided with the purchase o a

Sidekiq Z2 Plat orm Development Kit or a Matchstiq Z3u Plat orm Development Kit.

2 Legal Considerations

Sidekiq or Matchstiq radio cards are distributed all over the world. Each countr has its own

laws governing the reception and/or transmission of radio frequencies. The user of Sidekiq or

Matchstiq radio cards and associated software is solel responsible for insuring that it is used

in a manner consistent with the laws of the jurisdiction in which it is used. Man countries,

including the United States, prohibit the reception and/or transmission of certain frequenc

bands, or receiving certain transmissions without proper authorization. Again, the user is

solel responsible for the user's own actions in using Sidekiq or Matchstiq radio cards and

other Epiq Solutions' products.

3 Proper Care and Handling

Each unit is ully tested by Epiq Solutions be ore shipment, and is guaranteed unctional at the time it

is received by the customer, and ONLY AT THAT TIME. Improper use o the Sidekiq or Matchstiq unit

can cause it to become non- unctional. In particular, a list o actions that may cause damage to the

hardware include the ollowing:

•Handling the unit without proper static precautions (ESD protection) when the housing is

removed or opened up

•Inserting or removing Sidekiq or Matchstiq rom a host system when power is applied to the

host system

•Connecting a transmitter to the RX port without proper attenuation – see the Speci ications

section or details on maximum RF signal input levels

•Executing custom so tware and/or an FPGA bitstream that was not developed according to

guidelines

The above list is not comprehensive, and experience with the appropriate measures or handling

electronic devices is required.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

8

4 Introduction

The Sidekiq and Matchstiq Plat orm Development Kit (PDK) provides the ability or users to create

their own custom applications. This can be accomplished by customizing so tware or the RTL code

that con igures the FPGA. This manual gives an overview o the FPGA re erence design, with the

intention o empowering the user to build upon the design to create custom applications.

This document describes the unctionality o the Sidekiq and Matchstiq PDK re erence design that

was/is designed, developed, and supported by Epiq Solutions. The standard Sidekiq Z2 Evaluation

Kit (EVK) bitstream was/is designed, developed, and supported by Analog Devices' Industrial I/O (IIO)

and their open source ecosystem. Documentation and support or the IIO design is not provided by

Epiq Solutions. The Sidekiq Z2 PDK re erence design and the Matchstiq Z3u re erence design does,

however, utilize certain critical components rom the Analog Devices' IIO design, and details or

building both the EVK (Sidekiq Z2 only) and PDK components to achieve a inal bitstream is described

in Section 8.

Detailed in ormation about the so tware environment, including how to create custom so tware

applications, can be ound in a separate document, the Sidekiq So tware Development Manual [2],

which can be downloaded rom the Epiq Solutions support website

(http://www.epiqsolutions.com/support [3]).

In addition, the details o the hardware itsel and system design o the unit is outside the scope o this

document. For more details about the hardware, please download and review the Sidekiq Z2

Hardware User's Manual [4] or the Matchstiq Z3U Hardware User's Manual [6]. It is strongly

recommended that the user read these documents thoroughly be ore attempting to dive into FPGA

development.

This manual is meant to concisely describe the FPGA re erence design, but it is important or even an

experienced developer to spend time evaluating the actual design (i.e. RTL source code), perhaps

even while digesting the in ormation presented here. The sections o the manual were intentionally

created to align with the basic hierarchy o the design, and the source code itsel is commented and

will act as a supplement to the in ormation provided here.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

9

5 References

[1] Epiq Solutions Website

https://epiqsolutions.com

[2] SDK Documentation

Sidekiq_Software_Development_Manual_for_x.xx.x.pdf

Available at: https://epiqsolutions.com/support

[3] Epiq Solutions Support Website

https://epiqsolutions.com/support

[4] Sidekiq Z2 Hardware User's Manual

Sidekiq_Z2_Hardware_Users_Manual_vx.x.pdf

Available at: https://epiqsolutions.com/support

[5] Analog Devices, Inc. IIO and Support

www.analog.com

[6] Matchstiq Z3u Hardware User Manual

Epiq-Solutions-Matchstiq-Z3u-Hardware-User-Manual_vx.x.pdf

Available at: https://epiqsolutions.com/support

[7] Sidekiq Z2 Getting Started Guide

Z2 Getting Started Guide.pdf

https://epiqsolutions.com/support

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

10

6 Terms and Definitions

Term Definition

ADC Analog to Digital (A/D) converter

DAC Digital to Analog (D/A) converter

DSP Digital Signal Processing

EVK Evaluation Kit

FIFO First In First Out

FPGA Field Programmable Gate Array

FRC Free-running counter

IIO Industrial I/O (Analog Devices, Inc.)

I/Q In-Phase / Quadrature Phase

IP Intellectual Property

MHz Megahertz

PC Personal Computer

PDK Plat orm Development Kit

RF Radio Frequency

Rx Receive

SDR So tware De ined Radio

Tx Transmit

Table 1: Terms and Definitions

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

11

7 FPGA Reference Design

7.1 Overview

The Sidekiq and Matchstiq PDK provides a complete FPGA re erence design that enables a user to

quickly and e iciently create custom applications with a Xilinx Zynq-7000 xc7z010clg225-2 device or

the Z2 or with a Xilinx ZynqUs+ xc7z010-clg225-1 or the Z3U. On each plato rm, the IIO data

inter ace is used to move data between the Zynq processor and the FPGA.

The unmodi ied re erence design provides a ull FPGA implementation to low raw Rx I/Q samples

rom one ADC channel to the host Zynq processor and to transmit rom the host Zynq processor to the

RF chip via an FPGA channel o Tx data.

The PDK structure is created with the ease o the end-user in mind.

The Rx path trans ers baseband I/Q samples which are received rom an Analog Devices RFIC

Transceiver. These samples pass through a DC o set correction block (which can be toggled on/o

by so tware), then into a processing block which allows the user to process, timestamp, and trans er

the samples via an IIO FIFO inter ace to the Zynq processor. In the re erence design, the user

application processing block can unction as a simple pass-through which timestamps and drives the

IIO FIFO with no changes to the samples. In this ormat, the 12-bit I and 12-bit Q components are

sign-extended to 16 bits, or a 32 bit wide data bus. The “packed mode” (where 12 bit samples can be

packed to ully utilize the 32 bit bus) available on some o the other plat orms, is not currently available

on the Sidekiq Z plat orms.

On the Tx side, I/Q samples are trans erred rom the host system to the FPGA over IIO directly into

the RFIC DAC inter ace. The user has the ability to process Tx i so desired. Similar to the receive

side, transmit data can be pushed down in 16-bit sign extended mode or packed mode. Non-IQ data

o an arbitrary ormat can also be sent down and processed in the FPGA or the user to process and

transmit as desired.

In Figure 1, red blocks are available in RTL, but should not be modi ied. Yellow blocks should not

require modi ication, but certain applications may necessitate changes. Green blocks are the intended

targets or user modi ication.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

12

Figure 1: Sidekiq Z2 Simplified Block Diagram

7.2 Top Level

The Top Level block, sidekiq_z2_top (Sidekiq Z2 and Matchstiq Z3u share the some top level RTL ile)

is the top-level RTL and instantiates various blocks. This section will serve to describe each block's

unctions and use. Sections that have more signi icant impact on a PDK user will be discussed in

greater detail.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

13

7.3 user_app

The user app and register inter ace are Verilog iles in which the majority o signal processing is

expected to be done. The user_app inter ace is designed to allow reuse through multiple Epiq SDR

plat orms. user_reg_i is a submodule o user_app, which allows the user to maintain and customize

their own register space. In most cases, only the user_app.v and user_reg_i .v will need to be

modi ied to create custom FPGA images with advanced signal processing capabilities. The user_app

is built in its own directory so multiple apps can be built, tested, and version controlled simultaneously

and independently. See Section 8.1.3 or more in ormation on building custom apps. The user_app

structure is designed to allow or portable signal processing blocks between multiple Epiq SDR

plat orms, including all Sidekiq and Matchstiq variants. This allows end users to share user_app

modules between plat orms and allow upgrades to uture plat orms with minimal rework required.

Figure 2: User App Block Diagram

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

14

7.3.1 user_app Signals

Several signals are provided to acilitate custom designs, some o which are not used in the stock

user_app.

host_clock is the host system clock, which runs at 100 MHz.

clk_tx_fb is a eedback clock used to drive the transmit path. It runs at the same rate as the sample

rate clock. It is discussed more in the user_app transmit section.

aux_clk is an always-on 100 MHz clock (assuming that the Zynq processor is up and running). It

provides a clock source even i the RF chip is not running or no external re erence is present. For

Sidekiq Z2 and Matchstiq Z3u, this is the same clock as the host_clock.

ref_clk is an accurate 40MHz clock shared with the RF chip. I no external re erence is present or i

the RF chip is turned o , this clock will not be present.

external_enable can be used as an external gating signal or transmit/receive. By de ault, it is wired at

the top level to allow so tware to start/stop transmitting on a PPS edge. I this unctionality is not

needed but custom external gating is desired, this signal can be used.

timestamp_rst used to reset timestamps and ree-running counters. Timestamps can also be reset by

so tware.

reg_rx_# is a per-channel control register that allows the user to monitor the state o the channel as

controlled by so tware. Values o user interest are:

Bit # (indexed rom 0) Value : 0 Value : 1

1 IQ Data lowing Test mode: counter data lowing

2 Rx Reset (No data should low) Rx Enabled

8 Tx continuous mode Tx timestamp mode

9 Tx FIFOs enabled Tx FIFOs reset

10 Passthrough mode Packed Mode

11 DC O set disabled DC O set enabled

Table 2: Rx Control Register

Bit 1 indicates i IQ data is lowing or i so tware has set test mode, which results in incrementing

counter data being placed on the I and Q data bus.

Bit 2 is especially important – when low, the user should not push data to the IIO inter ace and should

reset any data counters, as the IIO bus is inactive.

Bit 5 in reg_rx_a1 indicates i the RFIC is in single or dual channel mode. Only single channel mode is

supported or Sidekiq Z2 while dual channel mode is supported or Matchstiq Z3u.

Bit 8 indicates i the transmit path is sending data as soon as it arrives, or i it is waiting to transmit

data at a speci ic timestamp driven by so tware.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

15

Bit 9 acts similar to bit 2, but on the transmit path. When asserted, the transmit FIFOs in the IIO

inter ace block are in reset.

Bit 10 indicates i the channel is operating in passthrough mode, which sign-extends the 12 bit I and Q

data to 16 bits each. I high, packed mode is enabled, which keeps I and Q 12 bits, and packs in the

next portion o I Q data in. This requires so tware decoding when received by the host but allows or a

roughly 20% increase in throughput.

Bit 11 indicates i so tware has enabled or disabled the DC O set block, which acts on the IQ data

be ore entering the user_app.

7.3.2 Rx Path Inputs to user_app

I/Q samples, valid signals, and clocks are routed in to the user_app and can be modi ied within to

per orm user-desired DSP. The input ports related to I/Q samples used are:

[11:0] i_samples_in_#, q_samples_in_#

sample_clk_a

sample_valid_a_#

full_#

Sidekiq Z2 and Matchstiq Z3u supports one I/Q channel. While sample_valid is high, each rising

edge o the sample clock delivers a new sample consisting o twelve bits each o I and Q data. Each

channel must be enabled by so tware be ore the sample_valid signal will go high.

The ull lag is rom the IIO inter ace and is used to indicate that, while sample data lowing in may be

valid, there is no longer room in the IIO bu er to contain them. This may be due to incorrect IIO

signaling or may indicate the total data throughput on all active channels exceeds the IIO data trans er

rate.

Two counters are passed in, which are passed through to the register inter ace or use by so tware.

[63:0] frc_a_in, frc_sys_in

frc_a begins running when the channel associated with it is enabled. They continually increment as

long as an associated clock is running. They can also be reset using a so tware-programmable PPS

based reset or by user logic. On a sample rate change, this clock will temporarily be lost.

frc_sys is a system counter that runs whenever the 40MHz re erence clock is present. It is 64 bits

wide, and is normally driven by the 40 MHz re erence clock to ensure accurate timekeeping. It can be

reset using a so tware-programmable PPS based reset, or by user logic. This counter is continuous.

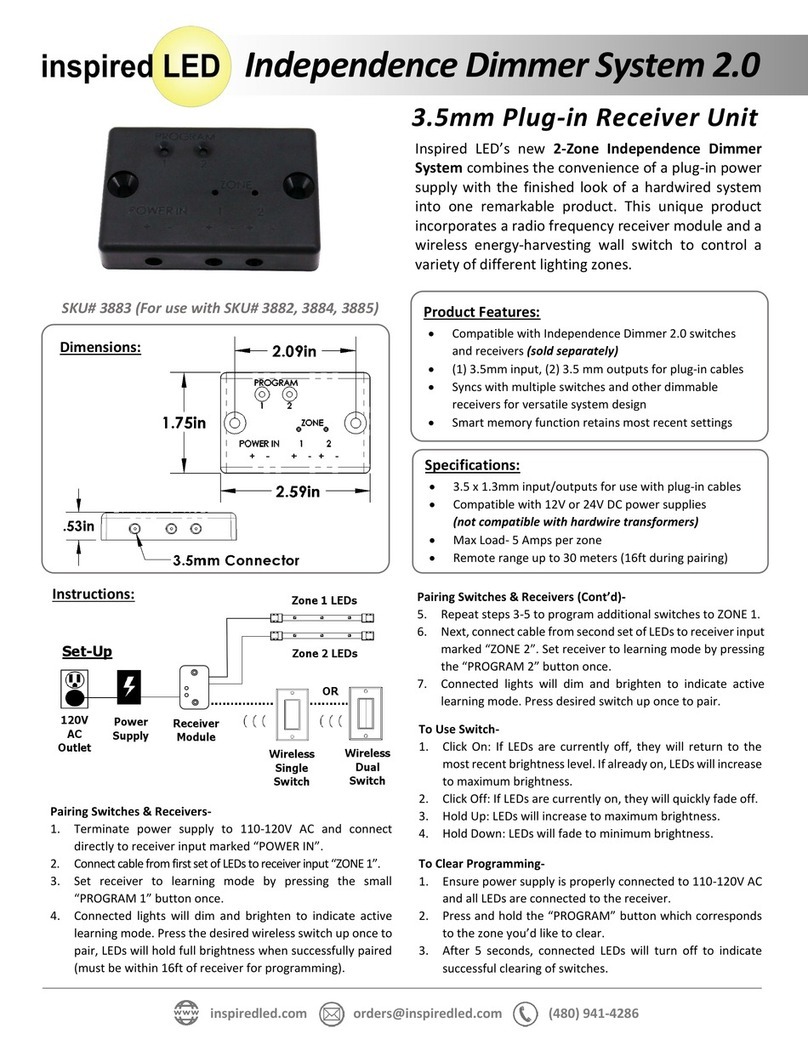

The ollowing diagram illustrates the relationship between sample_clk, samples_valid, IQ data, and the

ree-running counter. Note that samples are valid only when samples_valid is high, but the counter

increments as long as there is a valid clock.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

16

Figure 3: Sample Timing Diagram

7.3.3 Outputs from user_app

The user app drives data into a FIFO within the pcie_block NGC. Though the data can be thought o

as a logical stream, each PCIe trans er consists o 1024 words o 32 bit length each. There are 1018

words o data and 6 words o metadata or 1024 total words. The irst our words contain 64-bit

timestamps based on frc_a and frc_sys. The i th word contains channel and system control

in ormation. The sixth word is reserved or user de inition.

Note that the PCIe bus works on 1018 data increments – until this size is reached in the FIFO, no

data will be transmitted. I smaller data blocks are needed, the user must pad the remaining data

words until the 1018 data length is reached.

The ollowing signals are used to drive the PCIe FIFO:

[31:0] fifo_din_#

fifo_wren_#

sample_clk_a_out,

[63:0] frc_a_out, frc_sys_out

[31:0] user_metadata_#

fifo_din_# is a 32 bit wide data bus containing the data to be trans erred to so tware. In the stock app,

this contains unprocessed IQ data. Custom apps may process and place data in whatever ormat

desired on this bus. The fifo_wren_# signal must be driven high to push fifo_din_# data into the IIO

inter ace bu ers. The write enable does not need to be continuous – it can be asserted and

deasserted as necessary to push the proper processed data through. I tied high, data will

continuously be streamed into the IIO inter ace

The channel A1 clock is driven by sample_clk_a1_out. This is normally tied to sample_clk_a1, but

user applications may have other requirements.

I user blocks introduce a processing delay, the ree-running counters can be modi ied to account or

the delay. Alternatively, frc_x_out can be tied directly to frc_x_in and so tware can account or delays.

The metadata_# registers are optional. They contain up to 32 bits o user-supplied data which is

embedded within each data block trans erred over IIO. This allows users to trans er extra data with

each set o 1018 samples. The metadata is latched in on each the irst o the 1018 data words.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

1

sample_clk

samples_valid

i_sample I1 I2 I3 I4 I5 I6

q_sample Q1 Q2 Q3 Q4 Q5 Q6

frc n+0 +1 +2 +3 +4 +5 +6 +7 +8 +9

Figure 4: Sample User App to IIO Diagram

7.3.4 user_app Tx Interface

The Tx user inter ace allows so tware to pass down either IQ or other encoded data or processing to

the FPGA to then be transmitted via the RF DAC inter ace. The DAC inter ace will be described irst.

The inter ace to the RF chip is a 12 bit wide CMOS inter ace DDR bus, which means the clock driving

it will run at the sample clock rate. On the receive side, the data_clk is also running at the sample

clock rate. This is all transparent to user_app as it receives a sample_clock so each rising edge brings

in a new IQ pair. On the transmit side, the transmit clock is the same rate as the receive sample clock

rate, so each rising transmit clock will send a new IQ pair.

In passthrough mode, where each 32 bit data word tx_din_# coming rom IIO contains a single I and Q

pair and no additional data to be transmitted, tx_dac_en_in/out and tx_rd_en_in/out can be wired

together to pass data straight rom the IIO FIFO to the dac_i block.

The IIO inter ace can be modi ied i a user desires additional processing on transmit data. This

inter ace pulls data rom the IIO bus. To signal data is available, tx_dac_en_in goes high. On each

tx_rd_en_out strobe, data is pulled rom the IIO FIFO.

Note that i timestamp mode is used, the IIO inter ace will not drive tx_dac_en_in high until the proper

timestamp is reached. In continuous mode, data is provided as soon as it is available in the FIFO.

Continuous/timestamp mode is set by so tware.

Several other signals are available to assist in debug.

tx_ts_# indicates the timestamp (on the rc_# domain) that the transmit path is waiting on.

tx_err_# indicates that a timestamp error has occurred, which is typically when data is not be able to

be pushed down over the PCIe bus ast enough to transmit a packet at the correct time.

tx_empty_# indicates the PCIe FIFO is empty.

7.3.5 user_reg_if

Within the user_app, user_reg_i provides an address space to drive or read status o user logic. As

the unctionality o user_reg_i is nearly identical to reg_i , please see Section 7.4 or in ormation. The

code comments within user_reg_i serve to provide a template or adding user registers.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

18

sample_clk(i)

fo_din[31:0](o) 0 1 2 3 4 5 400 401 402 403 404

fo_wren(o)

metadata[31:0](o) meta1 meta2

data count (user) 0 1 2 3 4 1016 1017 0 1

7.4 reg_if / user_reg_if

reg_i and user_reg_i are Verilog ile that provides a register map or all FPGA unctions, starting at

address 0x8000 as re erenced by so tware. Addresses below 0x8000 will be visible on the bus, but

should be ignored, as they deal with AXI transactions beyond the scope o this document.

The R/W data bus is 32 bits wide, and 14 address lines are provided. The FPGA considers each 32

register a single address, while so tware addresses registers byte-wise. Logically, this results in the

so tware address's two least signi icant bits being truncated o . The irst so tware address, b1000

0000 0000 0000 (x8000), is seen as b10 0000 0000 0000 by the 14 address lines on the FPGA. The

second address, b1000 0000 0000 0100 (x8004) is seen as b10 0000 0000 0001 by the FPGA, and

so on.

Within the module, bits [9:6] on the address bus are used to denote the logical bank o the register,

and bits [5:0] denote the address. This mapping results in the third nibble o the address rom

so tware being the bank(i.e. x8000 is bank zero, x8100 is bank two, x8300 is bank three, and so on).

Banks 0-6 are used by the system, and it is recommended they not be modi ied, though PDK

customers do have the ability to do so. These banks are located in reg_i .v, which is instantiated in the

top level.

Bank 0 is a general purpose bank, and does not contain any clock domain crossing logic.

Banks 1-4 provide system control over each Rx/Tx channel, and are synced to the sample clock on

the channel domain.

Banks 5-6 are currently unused, but reserved.

Banks 7-9 are user register space, and are located with user_reg_i .v, which instantiated within

user_app.

Eight read and our write registers are provided in the example design in the 8700 register space, and

are not synced to any speci ic clock domain. They are driven by the PCIe clock. The user may

rename, add, or delete as desired to inter ace with user logic. I urther register customization is

desired, ollow the template ound in the source code. The provided read/write (so tware driven)

registers and read-only (FPGA driven) registers are:

SW Address (hex) FPGA Name R / R/W

0x8700 reg_7_0 R/W

0x8704 reg_7_1 R/W

0x8708 reg_7_2 R/W

0x870C reg_7_3 R/W

0x8710 reg_7_4 R

0x8714 reg_7_5 R

0x8718 reg_7_6 R

0x871C reg_7_7 R

Table 3: User Registers

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

19

Please note that bit zero o x8708 is currently used to illustrate how a timestamp reset can be driven

up to the top level via custom logic with a user_app register bit in the user_app. The ollowing line o

RTL is used or this in user_app.v:

assign timestamp_rst = user_reg_2_w[0];

I you do not want this unctionality and would like to be able to write to 0x8708 without it a ecting the

timestamps, replace the line o code in user_app.v with the ollowing:

assign timestamp_rst = 1'b0;

Banks 8 is synced to sample_clk_a via a FIFO. The write side o the FIFO is driven by the AXI

inter ace, and the read out rom the FIFO is driven by the respective sample_clk. This gives a block o

registers which can be used in sync-sensitive designs. It is recommended to only add registers and

not modi y the FIFO sync portion o the code. A template or adding registers is provided within the

comments o user_reg_i .v.

I custom clock syncs are desired, it is suggested to use the 8700 register space, and sync the desired

registers individually.

7.5 iio_data_if

Sidekiq Z2 and Matchstiq Z3u only supports one channel o Rx and one channel o Tx. Being able to

adjust the size o the Tx FIFO is not required like it is on older plat orms that use the PCIe inter ace.

However, the RTL can be customized to remove the one Tx channel to ree up some BRAM resources

i needed.

The instantiation o the iio_data_i occurs at the top level in sidekiq_z2_top.v. To remove the Tx

channel, simply edit this ile to set the TX_CAPABLE parameter to 1'b0 (de ault is 1'b1) or this

instantiation and then build the project.

7.6 timestamp_blo k

The timestamp_block.v is a Verilog ile which handles driving and resetting the ree-running counters

(FRC) which serve to time stamp the samples. It also controls signaling to start and stop

receipt/transmission o data based on a PPS signal.

Time syncing multiple units is handled primarily by so tware; see the Sidekiq So tware Development

Manual [2] or more in ormation.

As it relates to the FPGA, the user_app can drive a reset, which will clear all ree-running counters or

as long as it is held high.

There are two counters present rc_a and rc_sys. rc_a is driven by sample_clk_a, and rc_sys is

driven by the 40MHz re erence clock. As long as reset is not held, these counters will increment as

long as there is a clock present.

Sidekiq Z2 and Matchstiq Z3u FPGA Development

Manual

20

Other manuals for Sidekiq Z2

2

This manual suits for next models

1

Table of contents

Other Epiq Solutions Network Hardware manuals

Popular Network Hardware manuals by other brands

Peak

Peak PCAN-Router DR user manual

IPmitter

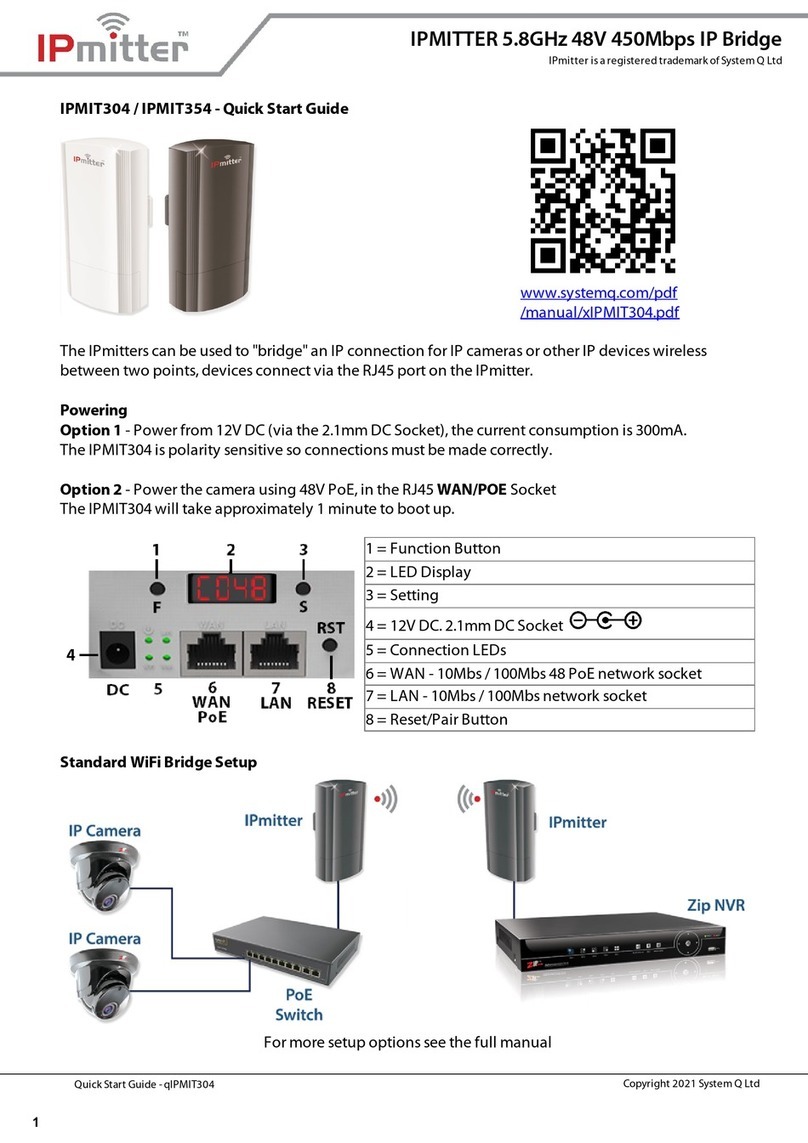

IPmitter IPMIT304 quick start guide

Tyco Electronics

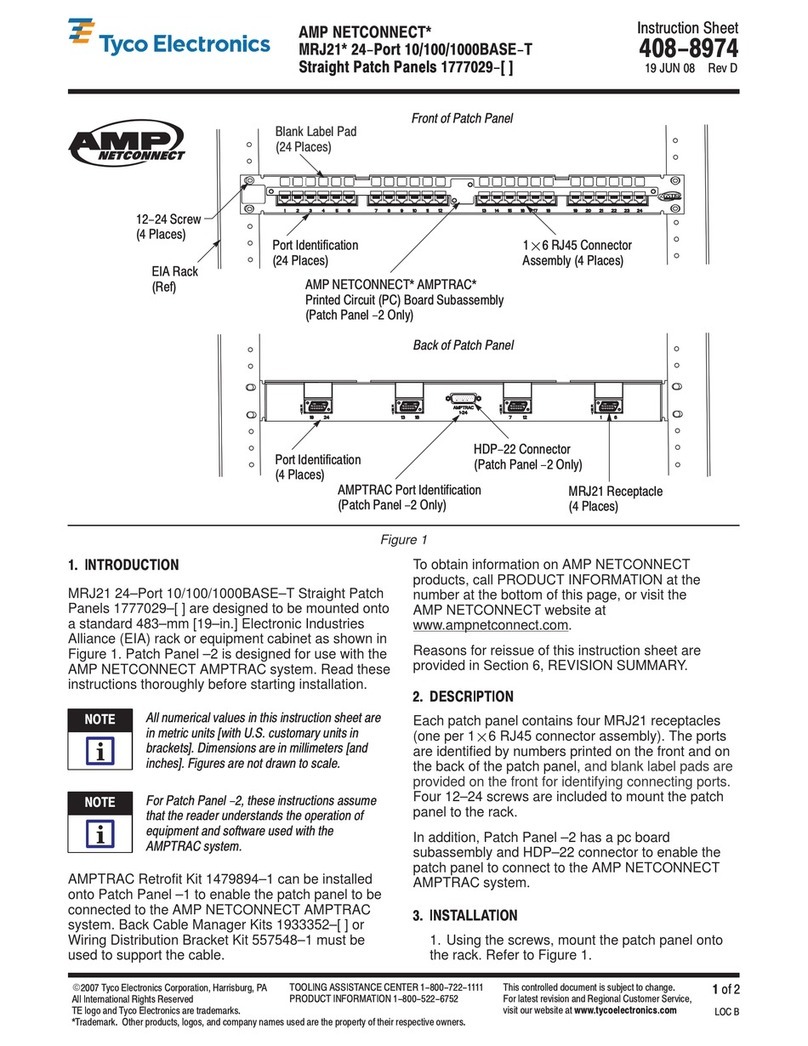

Tyco Electronics AMP NETCONNECT MRJ21 Series instruction sheet

Lenovo

Lenovo EZ Media & Backup Center quick start guide

Altronix

Altronix TROVE T2AGK78 installation guide

D-Link

D-Link DNR-2020-04P Quick installation guide