HP 13255 User manual

Other HP Control Unit manuals

HP

HP HP 81531A User manual

HP

HP HP 81554SM Owner's manual

HP

HP Synergy 480 Gen9 User manual

HP

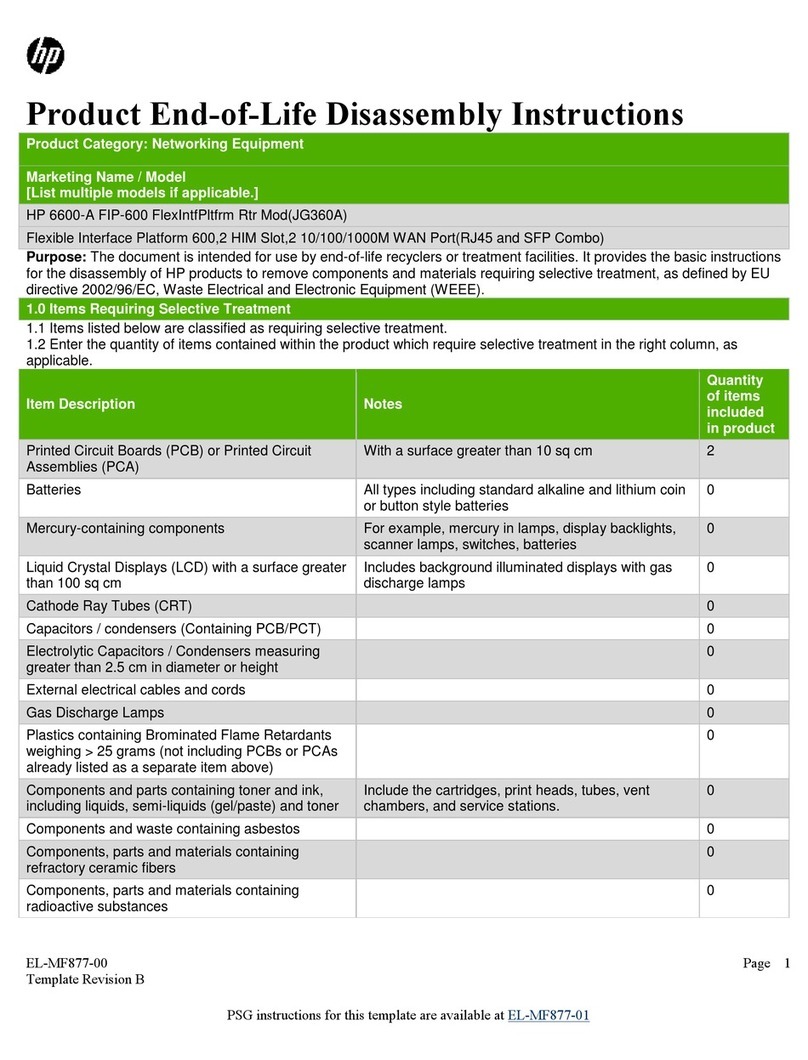

HP 6600-A FIP-600 FlexIntfPltfrm Rtr Mod Assembly instructions

HP

HP 3484A Service manual

HP

HP 13255 Manual

HP

HP DESKJET 1050 Product manual

HP

HP HP 83491A User manual

HP

HP 81541MM Owner's manual

HP

HP HP 81536A User manual

Popular Control Unit manuals by other brands

Festo

Festo Compact Performance CP-FB6-E Brief description

Elo TouchSystems

Elo TouchSystems DMS-SA19P-EXTME Quick installation guide

JS Automation

JS Automation MPC3034A user manual

JAUDT

JAUDT SW GII 6406 Series Translation of the original operating instructions

Spektrum

Spektrum Air Module System manual

BOC Edwards

BOC Edwards Q Series instruction manual

KHADAS

KHADAS BT Magic quick start

Etherma

Etherma eNEXHO-IL Assembly and operating instructions

PMFoundations

PMFoundations Attenuverter Assembly guide

GEA

GEA VARIVENT Operating instruction

Walther Systemtechnik

Walther Systemtechnik VMS-05 Assembly instructions

Altronix

Altronix LINQ8PD Installation and programming manual