Abstract

This paper is intended to clarify HP local I/O strategy for ProLiant servers. HP server I/O priorities

reflect the demands of IT managers. HP supports I/O technologies that protect customer investments

and extend I/O performance, flexibility, and reliability. This paper describes today’s parallel bus

architecture and explains why the industry is beginning a transition to PCI Express. It provides details

on PCI Express technology and information to help customers determine which I/O technology to use.

Introduction

There is constant pressure on the Peripheral Component Interconnect (PCI) bus to meet the I/O

bandwidth demands of data traffic traveling between increasingly powerful CPUs and I/O devices.

The PCI standard has continued to meet the needs of CPUs and I/O devices by increasing

performance while maintaining backward compatibility. Historically, server local I/O performance

has doubled almost every two years with a new phase of the PCI standard.

With the advent of faster and more complex I/O devices, PCI-X 1.0, which defined device speeds of

PCI-X 66 and PCI-X 133, was introduced to extend the performance and RAS (reliability, availability,

and serviceability) features of PCI technology in servers. PCI-X 1.0 leveraged the wide acceptance of

the PCI bus and doubled the maximum bandwidth to 1066 MB/s with a 64-bit, 133-MHz bus. In

2002, the PCI SIG extended the PCI-X 1.0 specification with PCI-X 2.0. The PCI-X 2.0 specification is

a smarter, more robust I/O technology that doubles and quadruples PCI-X bandwidth with two

additional device speeds: PCI-X 266 and PCI-X 533.

In 2002, the PCI-SIG also introduced a new physical implementation of PCI, called PCI Express,

which was originally optimized for desktop applications. With anticipated bandwidths in excess of

4 GB/s, PCI Express delivers the performance required for next-generation 10-Gb Ethernet adapters.

This paper begins with a summary of today’s parallel bus system and then describes PCI Express

technology. This paper also provides deployment and timeline information to help customers develop

a transition plan.

Today’s parallel bus system

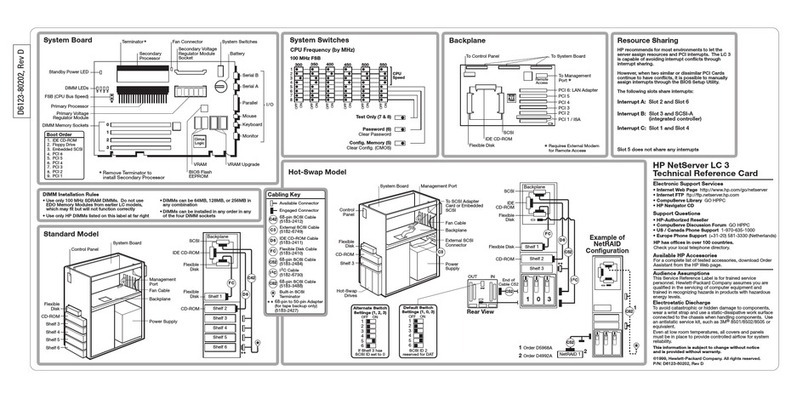

Today’s parallel bus system (PCI and PCI-X) uses bit-parallel, bi-directional, multi-drop connections

running at relatively low frequency (Figure 1). PCI and PCI-X send 32 or 64 data bits plus control

signals over the parallel bus. The number of pins required corresponds to the width of the bus: a

32-bit bus requires 50 to 60 pins (data plus control) and a 64-bit bus requires approximately

100 pins.

The number of devices sharing one bus shrinks as the speed of the bus increases. For example:

• 33-MHz PCI supports 5 or 6 slots.

• 66-MHz PCI-X supports 4 slots.

• 100-MHz PCI-X supports 2 slots.

• 133-MHz and higher PCI-X supports 1 slot.

2