SECTION 3CIRCUIT DESCRIPTION

3-1RECEIVER CIRCUITS

3-1-1 VHF ANTENNA SWITCHING CIRCUIT

(PA UNIT)

Incoming VHF signals from the antenna connector are

passed through aChebyshev Low-pass filter consisting of

L3, L4, L6, Cl 2, Cl 3, Cl 4, and Cl 5, and are fed to the

antenna switching circuit. While receiving, D2 is turned ON.

Receive signals from alow-pass filter are passed through

another filter consisting of Cl 0, L2 and Cl 7, and are fed to J1

on the MAIN UNIT.

3-1-2 VHF RF AMPLIFIER CIRCUIT (MAIN UNIT)

Signals from J1 are passed through the L1-L2 bandpass

filter, and are amplified by Q1. Amplified signals from Q1 are

passed through the L3-L4-L5 bandpass filter, and are mixed

with the local oscillator signal from the PLL circuit in Q2 to

produce afirst IF signal of 30.875MHz.

3-1-3 UHF ANTENNA SWITCHING CIRCUIT

(PA UNIT)

Incoming VHF signals from the antenna connector are

passed through both aChebyshev low-pass filter consisting

of LI 3, LI 4, C35, C36 and C37 and aChebyshev low-pass

filter consisting of L11, L13, C32, C33 and C34 before being

fed into the antenna switching circuit. While receiving, D5 is

turned OFF. Receive signals from the low-pass filter are

passed through another filter consisting of L10, C30, C39

and C40, and are fed to J3 on the MAIN UNIT.

3-1-4 UHF RF AMPLIFIER CIRCUIT (MAIN UNIT)

Signals from J3 are passed through atuned circuit

consisting of L1 1,C21 and C22, and the output is amplified

by Q5. The output from Q5 is passed through bandpass filter

L13, amplifier Q6, bandpass filter LI 5, and is mixed with the

local oscillator signal from the PLL UNIT to produce afirst IF

signal of 30.875MHz.

3-1-5 IF AMPLIFIER CIRCUIT (MAIN UNIT)

The first IF signal from the mixer is passed through the

L8-C1 2tuned circuit, is filtered by crystal filter Fit ,is passed

through the L9-C15 tuned circuit, and is amplified by Q4. D3

and D4 function as alimiter for strong signals. The amplified

signal from Q4 is fed to pin 16 of IC1. IC1 incorporates a

second oscillator, asecond mixer, alimiter and a

discriminator on asingle chip. The signal from pin 16 of IC1

is mixed with the second oscillator signal to produce the

455kHz signal at pin 3on IC1 .The 455kHz signal is filtered by

ceramic filter FI2 and is fed to pin 5of IC1 where it then

enters the limiter amplifier. The amplified signal is fed to the

discriminator through ceramic discriminator unit XI. The

audio signal exits from pin 9on IC1.

3-1-6 AUDIO AMPLIFIER CIRCUIT (MAIN UNIT)

The audio signal from pin 9on IC1 is amplified by Q10, is

filtered by active filter Q11, and is fed through J7 and the

VOLUME CONTROL to pin 1on 105. IC5 is the audio power

amplifier. The amplified audio signal from IC5 is fed to the

speaker through J10.

3-1-7 SQUELCH CIRCUIT (MAIN UNIT)

The audio signal from pin 9on IC1 is also fed to the noise

amplifier through C69, R50, J8, C70, and the SQUELCH

CONTROL and then is input to pin 10on IC1 .The amplified

noise signal exits from pin 11on IC1 ,is rectified by D1 1and

D12, and is controlled by 09 through R54.

3-1-8 S-METER CIRCUIT (MAIN UNIT)

S-meter signals from pin 5on IC1 are amplified by IC3

through C66 and R49, are passed through L20, are rectified

by D9 and DIO, and are fed to the LCD driver circuit on the

LOGIC AUNIT through J12. In the VHF mode, the band

signal turns ON Q12 to adjust the gain of IC3 by means of

R82, equalizing the S-meter level between VHF and UHF.

3-2TRANSMITTER CIRCUITS

3-2-1 MIC AMPLIFIER CIRCUIT (PLL UNIT)

The microphone output is fed into IC5A through C60andthe

08 amplifier. IC5A includes adifferential amplifier and a

limiter amplifier with R2 as the UHF deviation gain

adjustment and R3 as the VHF deviation gain adjustment.

Preemphasis of 6dB/octave is introduced between 300Hz

and 3kHz. The signal is then fed to the FM modulator in the

TX VCO UNIT through alow-pass filter consisting of IC5B,

R45, R46, R49, C51, C52, and C53.

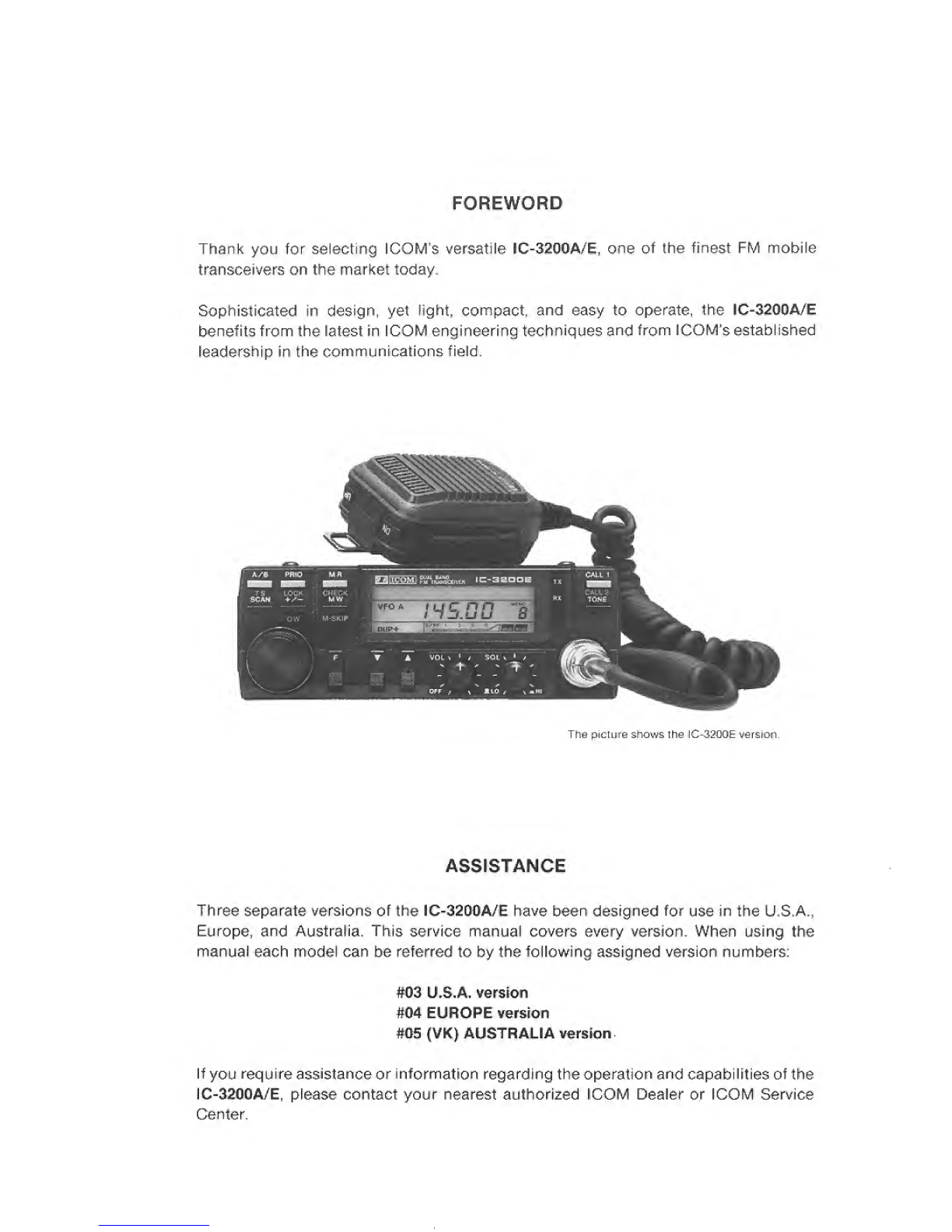

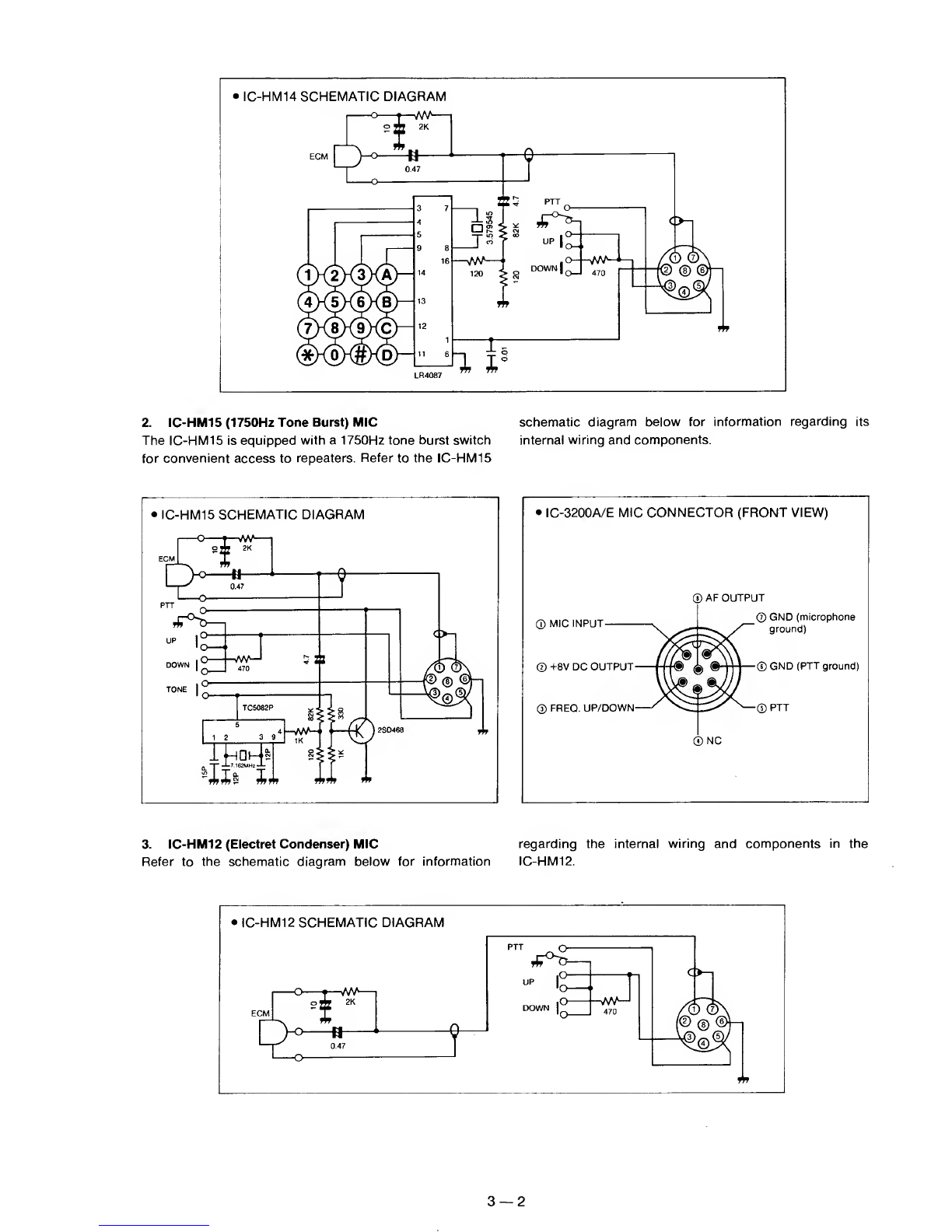

3-2-2 MICROPHONES USED WITH THE IC-3200A/E

The IC-3200A/Ecomesfactoryequipped with a high-quality

electret condenser microphone. The type of supplied

microphone varies with each transceiver model. The

microphone types are listed below.

IC-3200A (#03) ;IC-HM14 (DTMF Encoder)

IC-3200E (#04) ;IC-HM15 (1750Hz Tone Burst)

IC-3200A (#05) :IC-HM12

1. IC-HM14 (DTMF Encoder) MIC

Plug the IC-HM14 into the MIC CONNECTOR on the front

panel for immediate transceiver operation. If you wish to use

adifferent microphone with the IC-3200A, be sure it has the

proper output level before making any connections.

Particular care should be exercised when wiring adifferent

microphone since the internal electrical switching system in

the transceiver depends on proper connections being made.

See the diagram on page 3-2 for proper MIC wiring

instructions.

3— 1