REL 1.0

Page 4 of 53

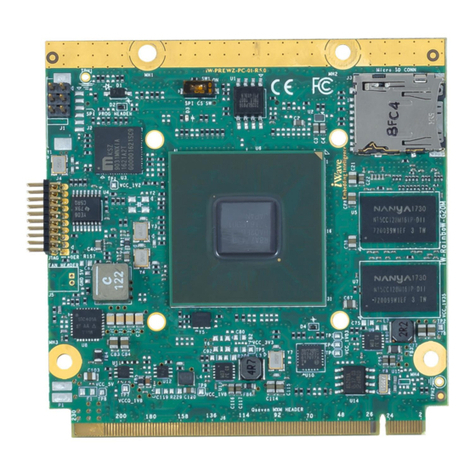

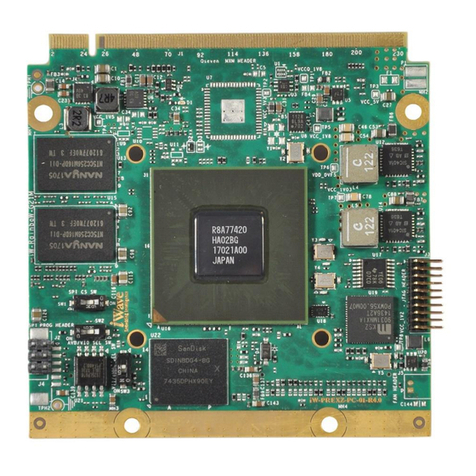

Cyclone V SoC Qseven SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

Table of Contents

1. INTRODUCTION ............................................................................................................................................ 7

1.1 Purpose ............................................................................................................................................................. 7

1.2 Qseven SOM Overview ..................................................................................................................................... 7

1.3 List of Acronyms................................................................................................................................................ 7

1.4 Terminlogy Description..................................................................................................................................... 9

1.5 References ........................................................................................................................................................ 9

1.6 Important Note ............................................................................................................................................... 10

2. ARCHITECTURE AND DESIGN....................................................................................................................... 11

2.1 Cyclone V SoC Qseven SOM Block Diagram....................................................................................................11

2.2 Cyclone V SoC Qseven SOM Features............................................................................................................. 12

2.3 Cyclone V SoC..................................................................................................................................................14

2.4 Boot Switches.................................................................................................................................................. 15

2.4.1 Boot Media Switch ...................................................................................................................................... 16

2.4.2 Boot Clock Switch (Optional)....................................................................................................................... 16

2.4.3 Reset Switch ................................................................................................................................................16

2.5 Memory...........................................................................................................................................................17

2.5.1 HPS DDR3 SDRAM with ECC ........................................................................................................................17

2.5.2 HPS QSPI Flash.............................................................................................................................................17

2.5.3 HPS EEPROM (Optional)..............................................................................................................................17

2.5.4 FPGA DDR3 SDRAM..................................................................................................................................... 17

2.5.5 FPGA Configuration Flash (Optional) ..........................................................................................................17

2.6 Other Features ................................................................................................................................................18

2.6.1 RTC Controller .............................................................................................................................................18

2.6.2 HPS JTAG Header......................................................................................................................................... 18

2.6.3 FPGA JTAG Header ...................................................................................................................................... 20

2.6.4 FPGA AS Header (Optional).........................................................................................................................21

2.6.5 Power IN Connector (Optional) ...................................................................................................................22

2.7 Qseven PCB Edge Connector...........................................................................................................................23

2.7.1 Qseven Interfaces from HPS........................................................................................................................24

2.7.2 Qseven Interfaces from FPGA High Speed Transceiver ............................................................................... 25

2.7.3 Qseven Interfaces from FPGA ..................................................................................................................... 25

2.8 Expansion Connector ...................................................................................................................................... 37

2.8.1 Expansion Connector Interfaces from FPGA................................................................................................38

3. TECHNICAL SPECIFICATION.......................................................................................................................... 43

3.1 Electrical Characteristics .................................................................................................................................43

3.1.1 Power Input Requirement ...........................................................................................................................43

3.1.2 Power Input Sequencing.............................................................................................................................. 43

3.1.3 Power Consumption ....................................................................................................................................44

3.2 Environmental Characteristics ........................................................................................................................45

3.2.1 Environmental Specification........................................................................................................................45