Table of Contents

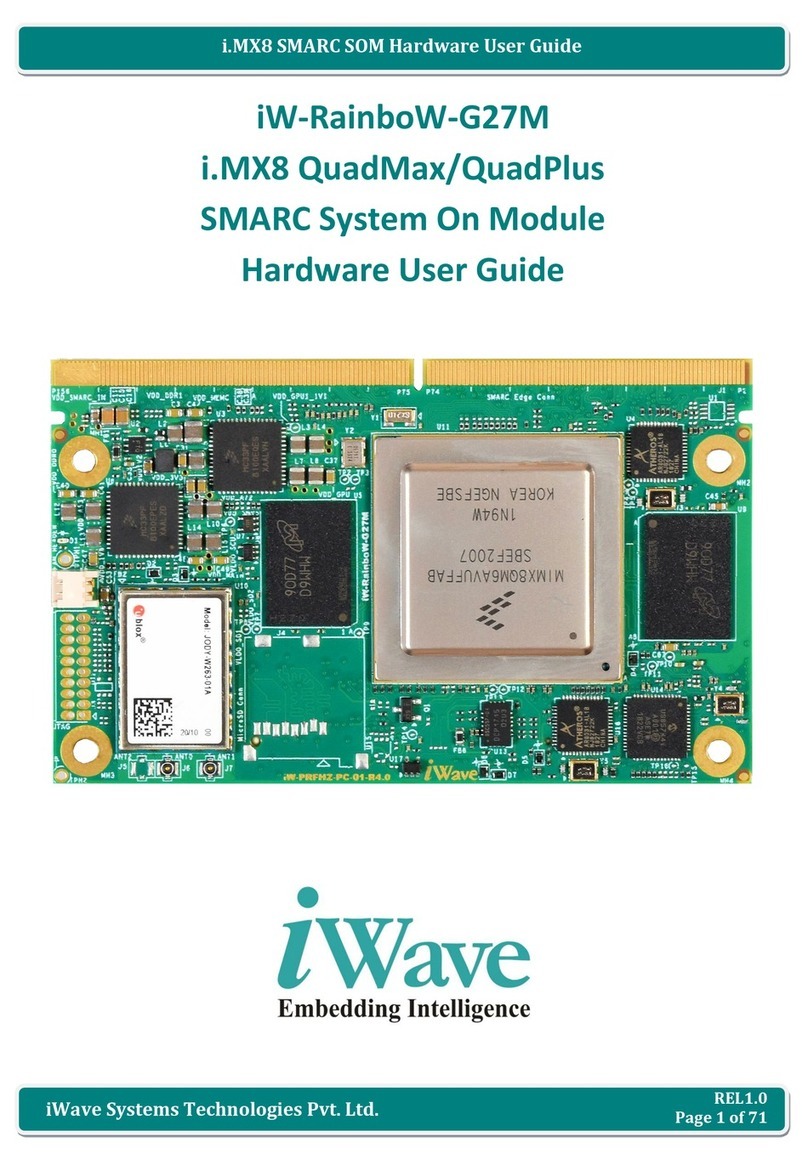

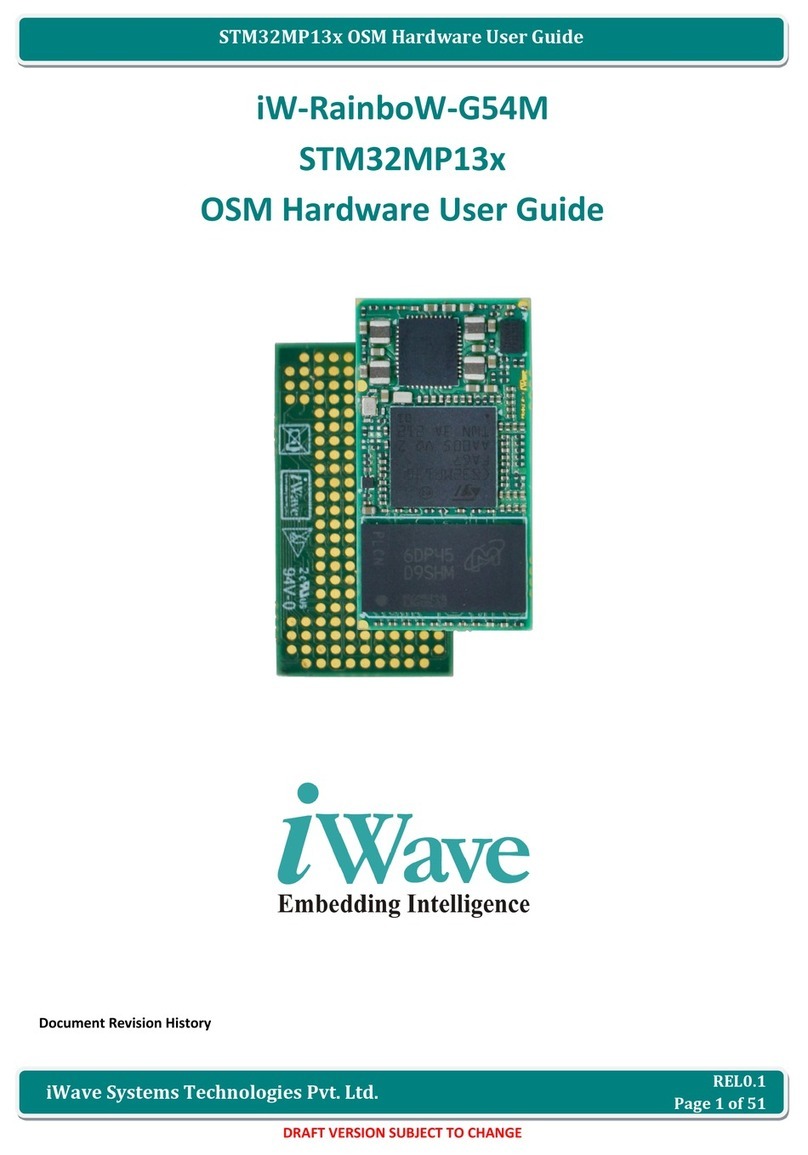

1. INTRODUCTION ............................................................................................................................................7

1.1 Purpose .............................................................................................................................................................7

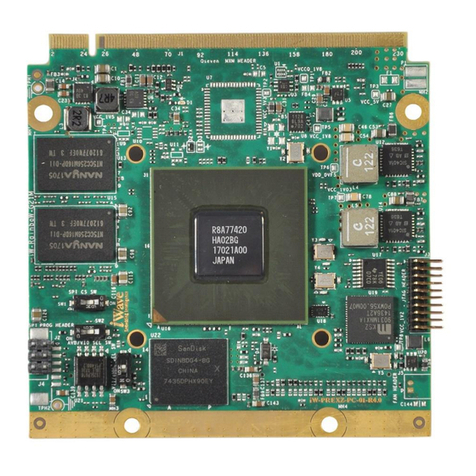

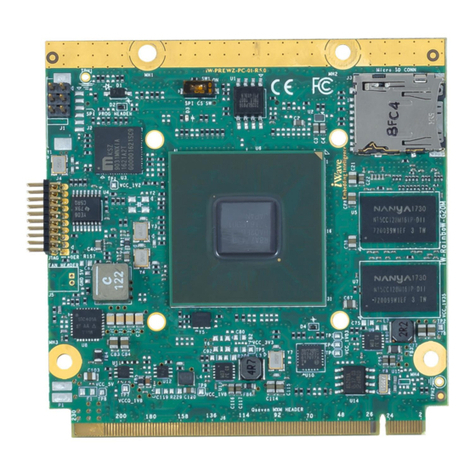

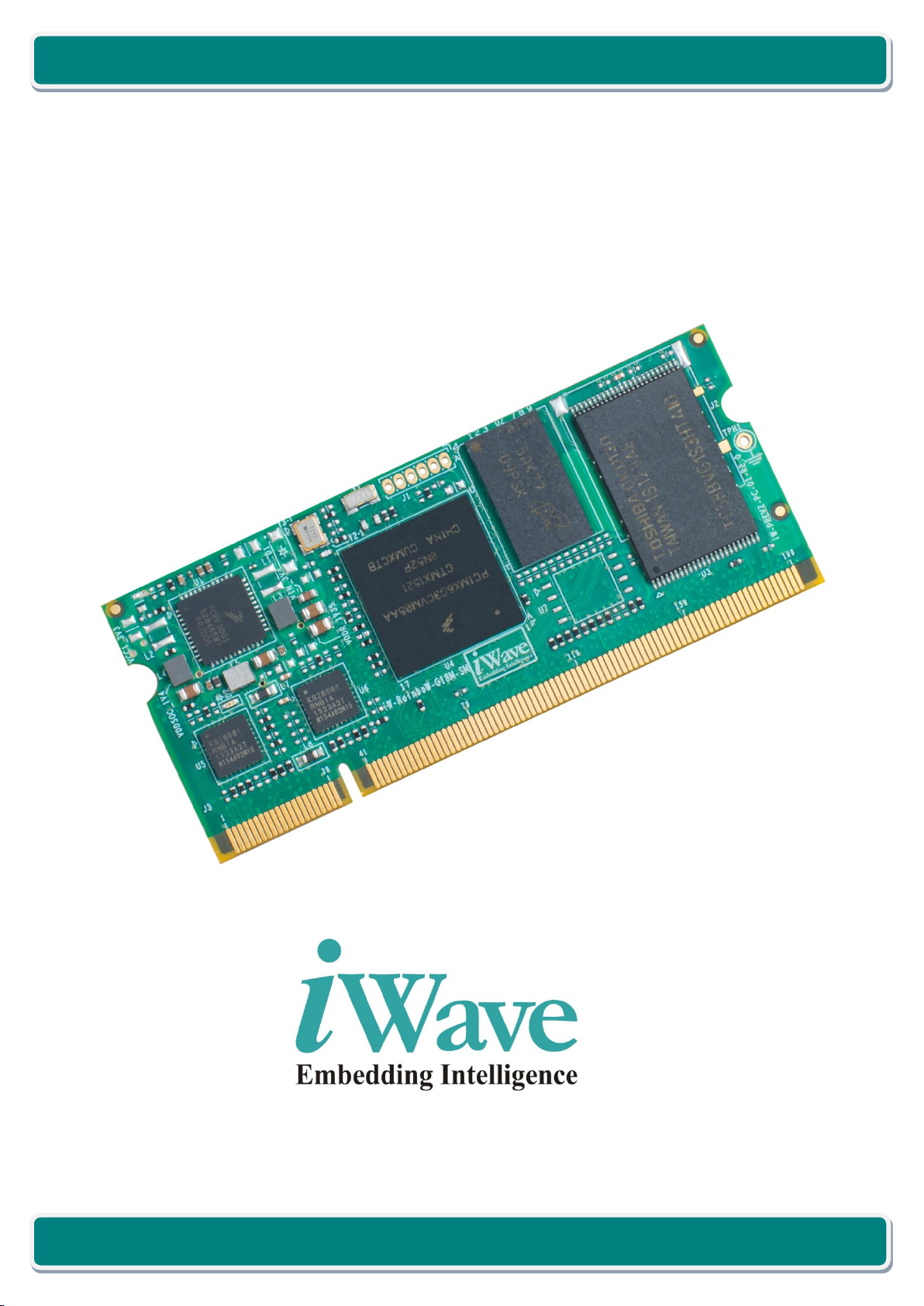

1.2 SODIMM SOM Overview................................................................................................................................... 7

1.3 List of Acronyms................................................................................................................................................7

1.4 Terminlogy Description.....................................................................................................................................9

1.5 References ........................................................................................................................................................9

1.6 Important Note ...............................................................................................................................................10

2. ARCHITECTURE AND DESIGN....................................................................................................................... 11

2.1 i.MX6UL/i.MX6ULL SODIMM SOM Block Diagram .........................................................................................11

2.2 i.MX6UL/i.MX6ULL SODIMM SOM Features...................................................................................................12

2.3 i.MX6UL/i.MX6ULL CPU ..................................................................................................................................14

2.4 PMIC................................................................................................................................................................16

2.5 Memory...........................................................................................................................................................16

2.5.1 DDR3L SDRAM.............................................................................................................................................16

2.5.2 NAND Flash .................................................................................................................................................16

2.6 SODIMM PCB Edge Connector........................................................................................................................17

2.6.1 UART Interface ............................................................................................................................................18

2.6.2 CAN Interface ..............................................................................................................................................18

2.6.3 SD Interface.................................................................................................................................................18

2.6.4 Parallel RGB Display Interface.....................................................................................................................18

2.6.5 Parallel Camera Interface............................................................................................................................19

2.6.6 I2S Audio Interface ......................................................................................................................................19

2.6.7 JTAG Interface .............................................................................................................................................19

2.6.8 USB 2.0 OTG Interface.................................................................................................................................20

2.6.9 Dual 10/100Mbps Ethernet.........................................................................................................................20

2.6.10 I2C Interface................................................................................................................................................21

2.6.11 PWM Interface ............................................................................................................................................21

2.6.12 Tamper Interface.........................................................................................................................................21

2.6.13 GPIO Interface.............................................................................................................................................21

2.6.14 General Purpose Clock.................................................................................................................................22

2.6.15 Boot Mode Signals ......................................................................................................................................22

2.6.16 Power Input.................................................................................................................................................23

2.6.17 Reset Signal.................................................................................................................................................23

2.6.18 Power Control Signal...................................................................................................................................23

2.7 Optional Features............................................................................................................................................36

2.7.1 eMMC Flash ................................................................................................................................................36

2.7.2 Micro SD Slot...............................................................................................................................................36

2.7.3 QSPI Flash....................................................................................................................................................36

2.7.4 PMIC OTP Header........................................................................................................................................37

2.8 i.MX6UL/i.MX6ULL Pin Multiplexing on SODIMM Edge .................................................................................38