Table of Contents

1. INTRODUCTION ............................................................................................................................................7

1.1 Purpose .............................................................................................................................................................7

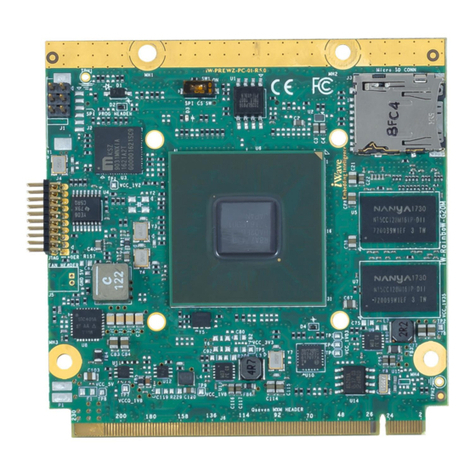

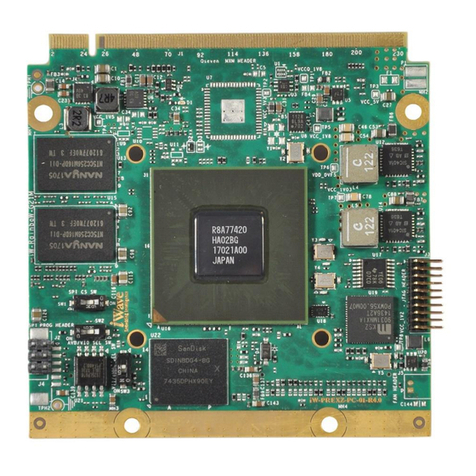

1.2 SMARC SOM Overview......................................................................................................................................7

1.3 List of Acronyms................................................................................................................................................7

1.4 Terminology Description...................................................................................................................................9

1.5 References ........................................................................................................................................................9

1.6 Important Note ...............................................................................................................................................10

2. ARCHITECTURE AND DESIGN....................................................................................................................... 11

2.1 i.MX8 QM/QP SMARC SOM Block Diagram ....................................................................................................11

2.2 i.MX8 QM/QP SMARC SOM Features .............................................................................................................12

2.3 i.MX8 CPU .......................................................................................................................................................14

2.4 PF8100 PMIC...................................................................................................................................................15

2.5 Memory...........................................................................................................................................................15

2.5.1 LPDDR4 RAM...............................................................................................................................................15

2.5.2 eMMC Flash ................................................................................................................................................15

2.5.3 Micro SD Connector (Optional) ...................................................................................................................15

2.5.4 FlexSPI Flash (Optional)...............................................................................................................................16

2.6 Network & Communiation..............................................................................................................................17

2.6.1 Wi-Fi and Bluetooth Interface.....................................................................................................................17

2.7 SMARC PCB Edge Connector...........................................................................................................................18

2.7.1 Gigabit Ethernet..........................................................................................................................................23

2.7.2 SERDES and MDIO Interface (Optional) ......................................................................................................25

2.7.3 SD Interface.................................................................................................................................................26

2.7.4 USB Interface...............................................................................................................................................26

2.7.5 PCIe Interface ..............................................................................................................................................28

2.7.6 SATA Interface.............................................................................................................................................29

2.7.7 MIPI CSI Camera..........................................................................................................................................29

2.7.8 HDMI/Display Port Interface.......................................................................................................................31

2.7.9 MIPI DSI/LVDS Display Interface .................................................................................................................33

2.7.10 Audio Interface............................................................................................................................................36

2.7.11 SPI Interface ................................................................................................................................................36

2.7.12 Data UART...................................................................................................................................................38

2.7.13 SMARC GPIOs ..............................................................................................................................................39

2.7.14 CAN Interface ..............................................................................................................................................39

2.7.15 I2C Interface................................................................................................................................................40

2.7.16 Control Signals ............................................................................................................................................41

2.7.17 Power and GND...........................................................................................................................................41

2.8 Expansion Connector (Optional).....................................................................................................................43

2.8.1 LVDS Interface (Optional)............................................................................................................................45

2.8.2 CAN Interface (Optional).............................................................................................................................46

2.8.3 USB3.0 Interface (Optional) ........................................................................................................................46