Table of Contents

1. INTRODUCTION ............................................................................................................................................8

1.1 Purpose .............................................................................................................................................................8

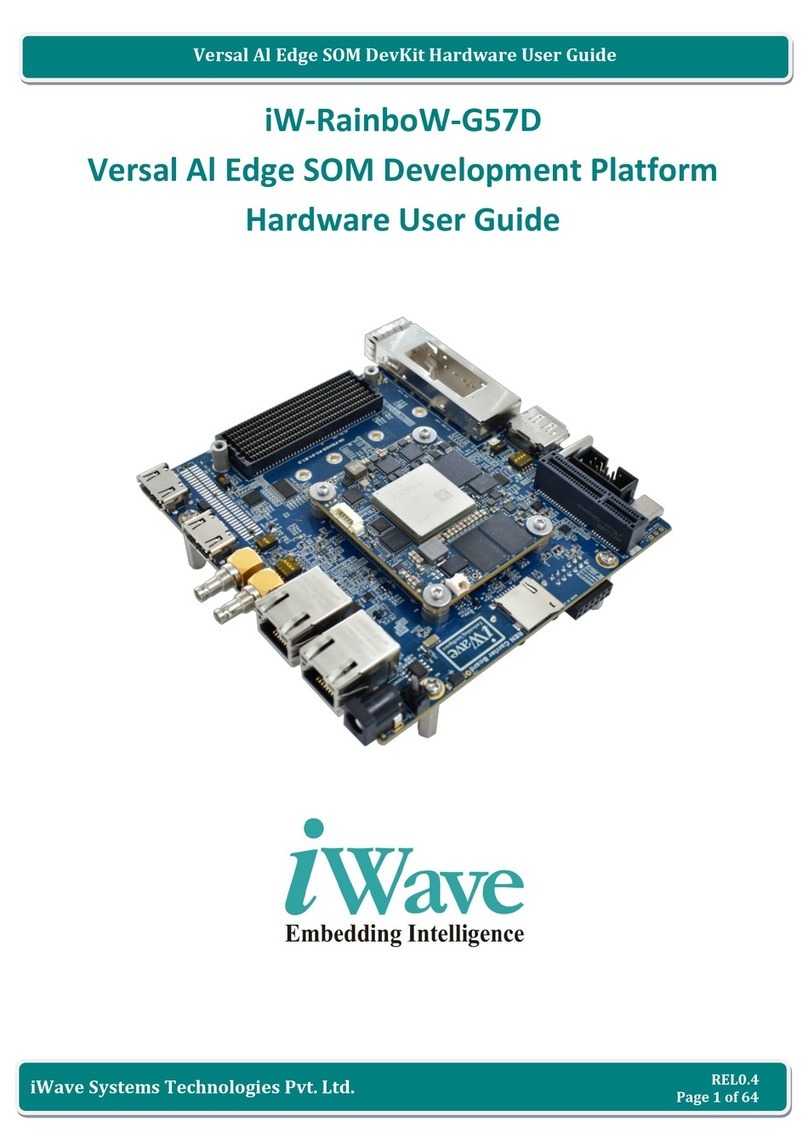

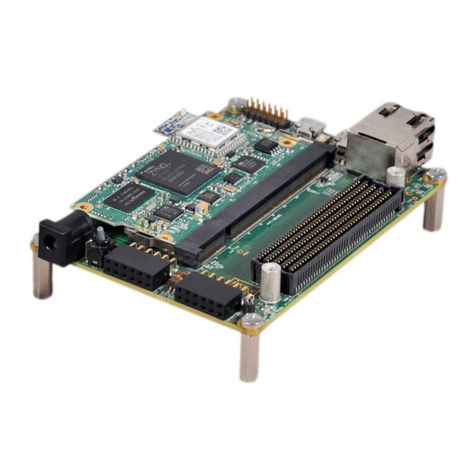

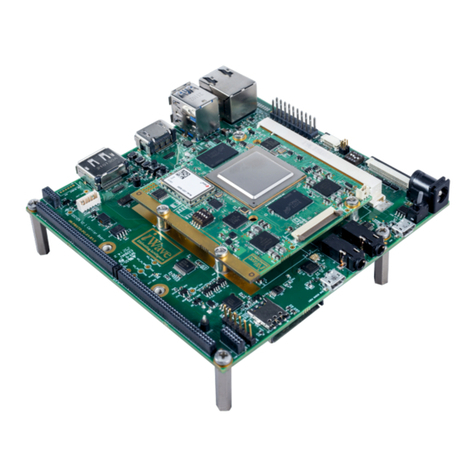

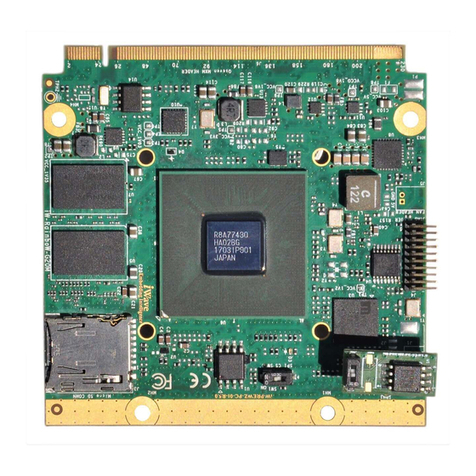

1.2 SBC Overview ....................................................................................................................................................8

1.3 List of Acronyms................................................................................................................................................8

1.4 Terminlogy Description...................................................................................................................................10

1.5 References ......................................................................................................................................................10

2. ARCHITECTURE AND DESIGN....................................................................................................................... 11

2.1 Zynq Ultrascale+ MPSoC SBC Block Diagram..................................................................................................11

2.2 Zynq Ultrascale+ MPSoC SBC Features ...........................................................................................................12

2.3 Zynq Ultrascale+ MPSoC .................................................................................................................................16

2.3.1 MPSoC Power..............................................................................................................................................18

2.3.2 MPSoC Reset...............................................................................................................................................19

2.3.3 MPSoC Reference Clock ..............................................................................................................................19

2.3.4 MPSoC Configuration & Status ...................................................................................................................20

2.3.5 MPSoC Boot Mode......................................................................................................................................20

2.3.6 MPSoC System Monitor/ADC......................................................................................................................21

2.4 PMIC with RTC.................................................................................................................................................21

2.5 Memory...........................................................................................................................................................22

2.5.1 DDR4 SDRAM for PS....................................................................................................................................22

2.5.2 DDR4 SDRAM for PL ....................................................................................................................................22

2.5.3 eMMC Flash ................................................................................................................................................22

2.5.4 EEPROM ......................................................................................................................................................22

2.5.5 Micro SD Connector (Optional)...................................................................................................................23

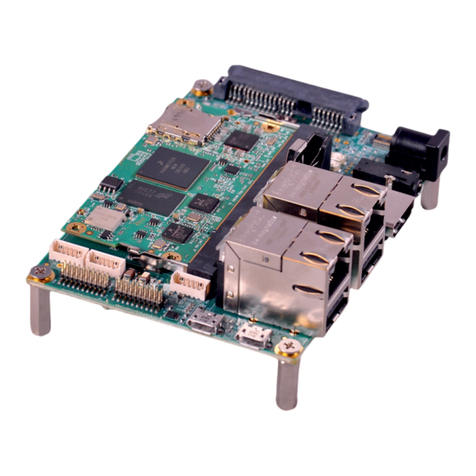

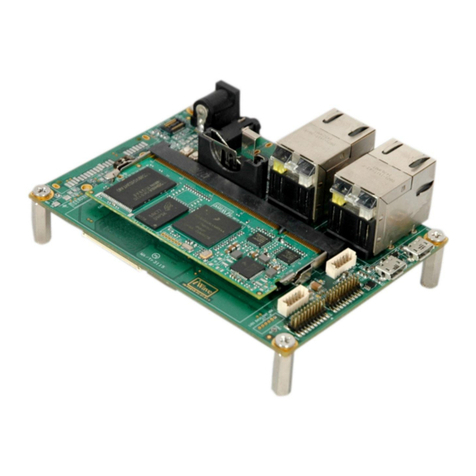

2.6 Fearures from PS Block ...................................................................................................................................24

2.6.1 Dual 10/100/1000Mbps Ethernet through RJ45 Magjack ..........................................................................24

2.6.2 WLAN & BT Module with Antenna connector............................................................................................25

2.6.3 Debug UART Header ...................................................................................................................................26

2.7 Features from PS-GTR.....................................................................................................................................27

2.7.1 Display Port Connector ...............................................................................................................................27

2.7.2 Dual USB3.0 Type A Jack .............................................................................................................................28

2.7.3 M.2 Key B Connector with SATA & USB3.0.................................................................................................29

2.8 Features from PL-GTH.....................................................................................................................................33

2.8.1 HDMI Input Connector................................................................................................................................33

2.8.2 HDMI Output Connector.............................................................................................................................34

2.8.3 SFP+ Connector...........................................................................................................................................35

2.8.4 3G/12G SDI IN (Optional)............................................................................................................................37

2.8.5 3G/12G SDI Output (Optional)....................................................................................................................37

2.9 Additional Features.........................................................................................................................................38

2.9.1 Clock Synthesizers.......................................................................................................................................38

2.9.2 JTAG Header................................................................................................................................................38

2.9.3 Fan Header..................................................................................................................................................40