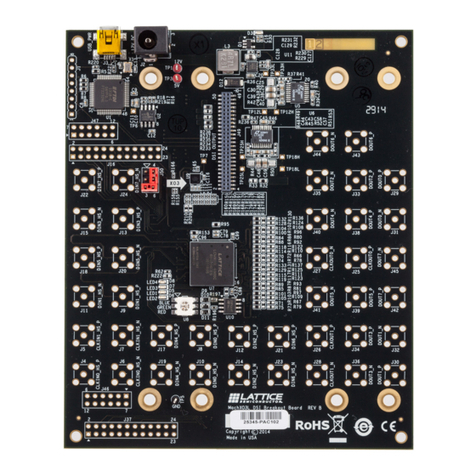

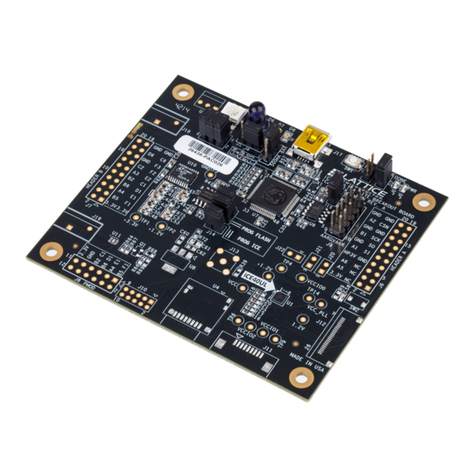

CrossLink LIF-MD6000 Master Link Board - Revision C

Evaluation Board User Guide

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

2 FPGA-EB-02018-1.0

Contents

Acronyms in This Document .................................................................................................................................................4

1. Introduction ..................................................................................................................................................................5

2. Headers and Test Connections .....................................................................................................................................7

3. Programming Circuit .....................................................................................................................................................8

3.1. Bridging Circuit ....................................................................................................................................................8

3.2. I2C Expander ........................................................................................................................................................9

4. Power Supply ..............................................................................................................................................................10

5. Status Indicators .........................................................................................................................................................12

6. SMA IO Link Board ......................................................................................................................................................13

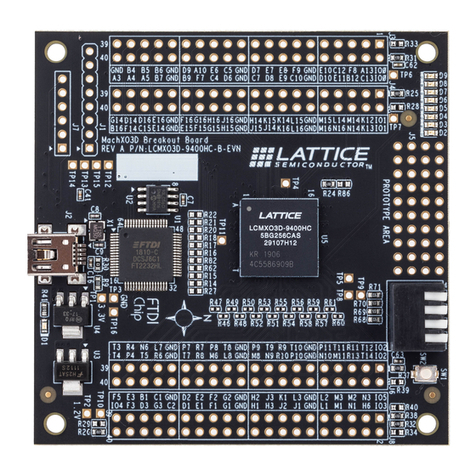

7. Breakout IO Link Board ...............................................................................................................................................15

8. Ordering Information..................................................................................................................................................18

References ..........................................................................................................................................................................19

Technical Support Assistance...............................................................................................................................................19

Appendix A. LIF-MD6000-ML-EVN-BRD Schematics ...........................................................................................................20

Appendix B. LIF-MD6000-ML-EVN-BRD Bill of Materials ....................................................................................................28

Appendix C. SMA-IOL-EVN-BRD Schematics .......................................................................................................................34

Appendix D. SMA-IOL-EVN-BRD Bill of Materials................................................................................................................35

Appendix E. B-IOL-EVN-BRD Schematics.............................................................................................................................36

Appendix F. B-IOL-EVN-BRD Bill of Materials .....................................................................................................................37

Revision History...................................................................................................................................................................38