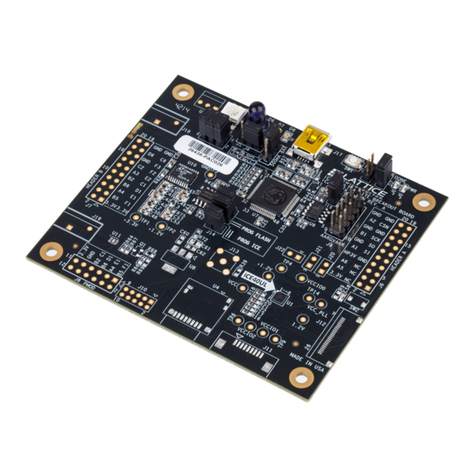

MachXO3D Breakout Board

User Guide

© 2019 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02084-0.90 3

Contents

Acronyms in This Document.................................................................................................................................................5

1. Introduction..................................................................................................................................................................6

2. Features........................................................................................................................................................................7

3. Storage and Handling ...................................................................................................................................................9

4. Software Requirements..............................................................................................................................................10

5. MachXO3D Device ......................................................................................................................................................11

6. Demonstration Design................................................................................................................................................12

6.1. Running the Demonstration Design ..................................................................................................................12

6.2. Download Demo Designs ..................................................................................................................................13

6.3. Programming a Demo Design with the Lattice Diamond Programmer.............................................................14

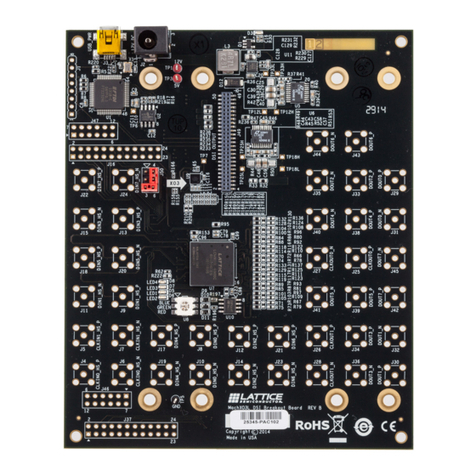

7. MachXO3D Breakout Board........................................................................................................................................15

7.1. Overview ...........................................................................................................................................................15

7.2. Subsystems........................................................................................................................................................16

7.2.1. Clock Sources ................................................................................................................................................16

7.2.2. Expansion Header Landings ..........................................................................................................................16

7.2.3. MachXO3D FPGA ..........................................................................................................................................22

7.2.4. Programming Interface Circuits....................................................................................................................22

7.2.5. LEDs...............................................................................................................................................................23

7.2.6. Power Supply ................................................................................................................................................23

7.2.7. Test Points ....................................................................................................................................................23

7.2.8. USB Programming and Debug Interface .......................................................................................................23

7.3. Board Modifications..........................................................................................................................................24

7.3.1. Bypassing the USB Programming Interface ..................................................................................................24

7.3.2. Applying External Power...............................................................................................................................24

7.3.3. Measuring Bank and Core Power .................................................................................................................24

7.4. Mechanical Specifications.................................................................................................................................24

7.5. Environmental Requirements ...........................................................................................................................24

8. Troubleshooting .........................................................................................................................................................25

8.1. LEDs Do Not Flash .............................................................................................................................................25

8.2. USB Cable Not Detected ...................................................................................................................................25

8.3. Determine the Source of a Pre-programmed Device........................................................................................25

9. Ordering Information .................................................................................................................................................26

Schematics................................................................................................................................................27

Bill of Materials.........................................................................................................................................35

References..........................................................................................................................................................................37

Lattice Semiconductor Documents.................................................................................................................................37

Revision History ..................................................................................................................................................................38