Certus-NX Versa Evaluation Board Demo

User Guide

© 2021 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

6 FPGA-UG-02133-1.1

1. Introduction

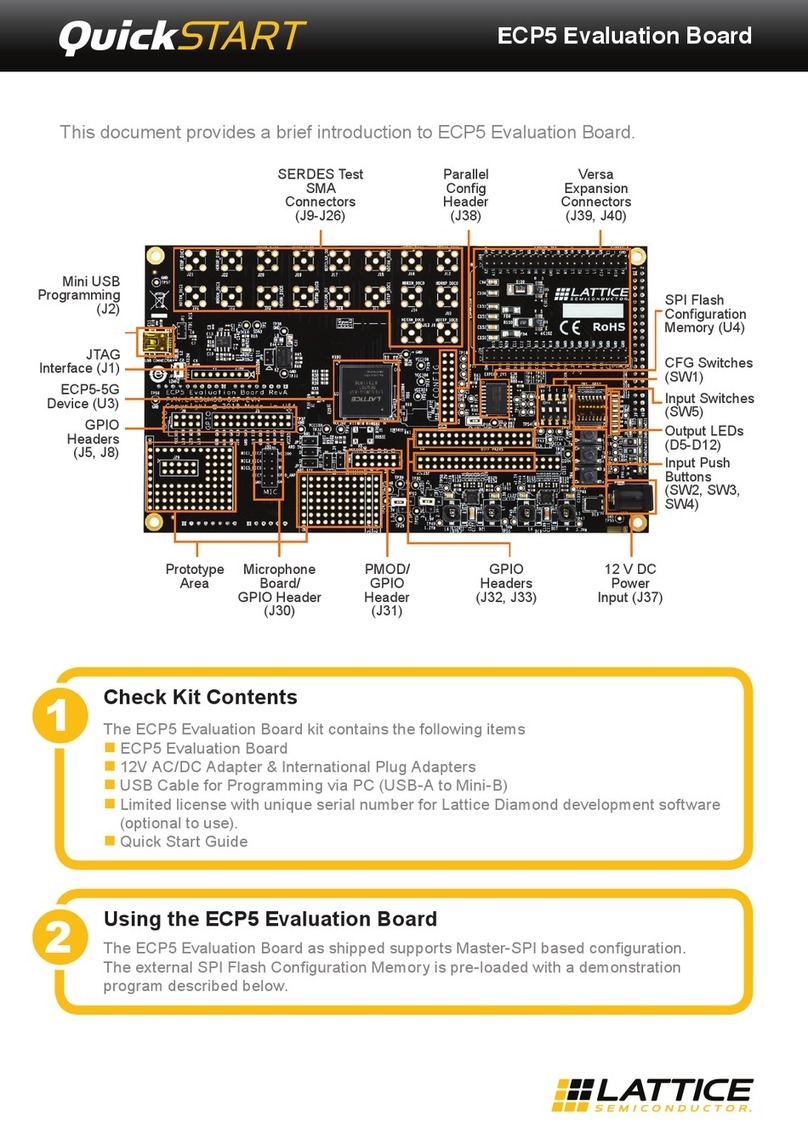

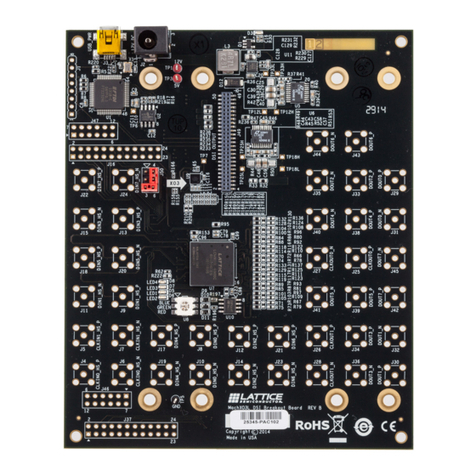

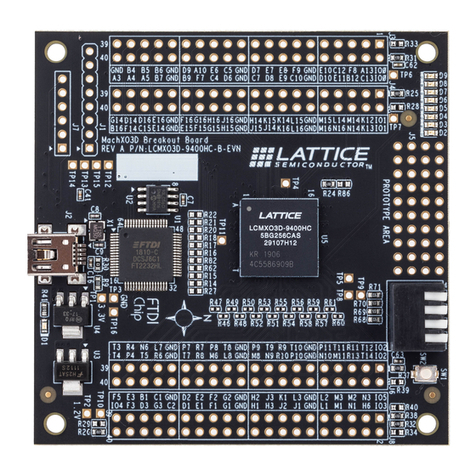

This guide describes how to start using the Certus™-NX Versa Evaluation Board, a low-cost platform for demonstrating

the PCI Express® reference design and for evaluating solutions for your specific application.

The Certus-NX Versa Evaluation Board features the Certus-NX FPGA in the 256-ball caBGA package, which is built on

the Lattice Nexus™ FPGA platform using low power 28 nm FDSOI technology. The board can expand the usability of the

Certus-NX FPGA with DDR3, soft D-PHY, 1 Gbps Ethernet and 1× PCIe (Gen2) channel. Board resources such as jumpers,

LED indicator, push button, and switch are available for user-defined applications.

This guide familiarizes you with the process of setting up your PCI Express development environment. It is assumed

that you do not have any associated tools installed on your system.

The demos discussed in this document include the PCI Express Basic Demo and PCI Express Memory Access Demo.

1.1. Learning Objectives

After completing the steps in this guide, you will be able to perform the following:

Set up the Certus-NX Versa Evaluation Board and become familiar with its main features

Install all applicable development tools and PCI Express demos

Establish communication between the Certus-NX Versa Evaluation Board through the PCI Express link

Run the PCI Express Basic Demo that allows you to control a 7 segment LED on the Certus-NX Versa Evaluation

Board. This demo is included in the user interface.

Run the PCIe Memory Access Demo, which allows you to manipulate the onboard memory of the FPGA through

the PCIe slot. This demo is included in the user interface.

Use what the demo teaches you about designing Lattice PCI Express solutions.

Modify and rebuild the PCI Express Basic Demo.

Become familiar with the software development tools and major design flow steps employed in this kit.

Use other existing documentation in conjunction with this guide.

This document assumes that you have already installed the Lattice Radiant™design software. This document covers

some of the basic of function of Lattice Radiant. If you would like to learn more about Lattice Radiant, refer to the

Radiant Help system.

1.2. Linux Version of this Demo

On the Lattice Semiconductor website, you can download an archive of the files needed to run this demo on Ubuntu

18.04.6 LTS. The steps necessary to complete the Linux version of this demo are provided in the Software Setup on a

Linux Machine section.