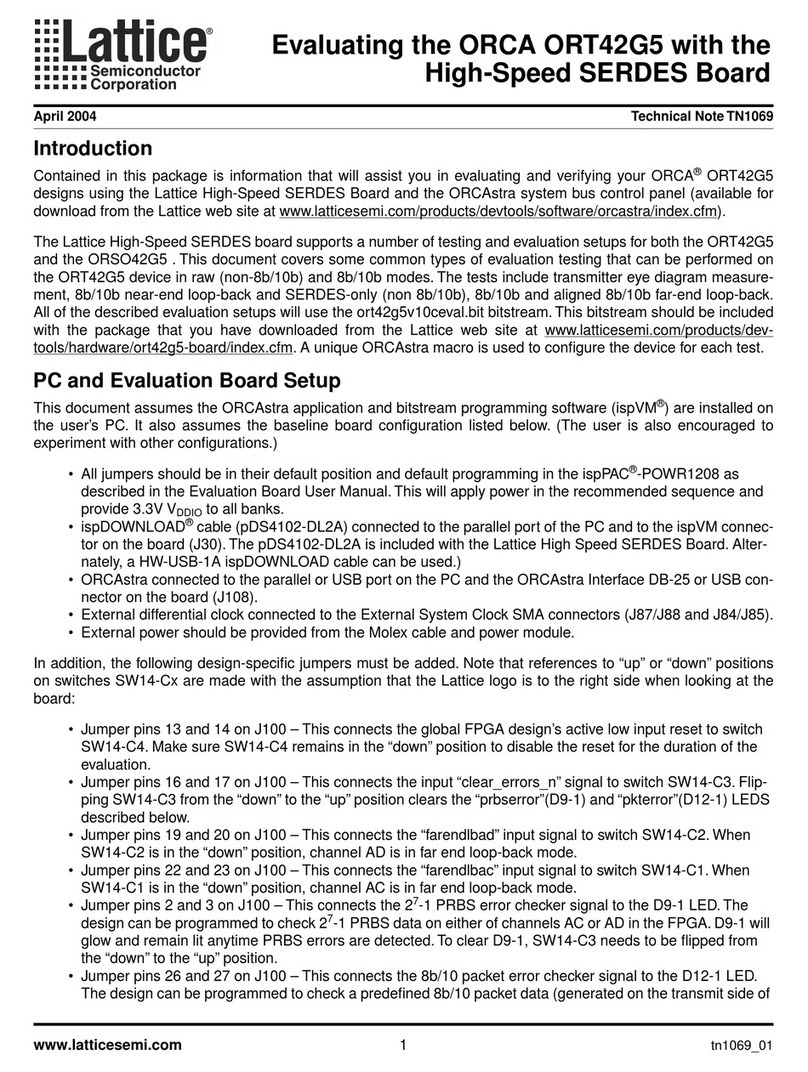

Evaluating the ORCA ORSO42G5 with the

Lattice Semiconductor High-Speed SERDES Board

9

Aligned SONET FELB

1. Connect the system as shown in Figure 8.The data SMA cables should be connected to the HDIN_Ax and

HDOUTN_Ax SMA connectors on the board.

2. Power-up the system.

3. Start the clock generator to provide a nominal 155.52MHz CML reference clock.

4. Download the orso4_felb6.bit bitstream into the ORSO42G5.

5. Run the sonet_felb.fpm macro using the pull-down menu in the ORCAstra application.This macro will reset

the channels and set up the AC and AD channels in Aligned SONET mode.

6. Begin transmitting and analyzing SONET data from the data source.

7. If at any point the REFCLK or data is stopped, the SERDES channel may need to be reset to reacquire

data lock.This can be done by re-running the sonet_felb.fpm macro using the ORCAstra application.

Once the system is set up and running in a FELB configuration, the ORSO42G5 device can be manipulated to vary

performance or inject errors into the system.Using the ORCAstra application, the user can enable features such as

pre-emphasis, half-amplitude and half-rate modes and observe the impact on performance using the analysis

capabilities of the external data source.

The SONET mode of the ORSO42G5 device has a per-channel selection for AUTO_TOH mode. The ORCAstra

application can be used to control this selection.When AUTO_TOH mode is enabled, the Tx SONET block inserts

all of the TOH bytes in the SONET frame. This mode overwrites any default TOH values. If AUTO_TOH mode is

used, the SONET scrambler/descrambler must also be used.

An AUTO_SOH mode can also be selected using the ORCAstra application.In this mode, A1/A2 and/or B1 bits are

optionally inserted by the core.All other TOH bits are passed transparently from the FPGA logic.

In the AUTO_TOH and AUTO_SOH modes, the user can use the ORCAstra control panel to manipulate all of the

Tx features in the ORSO42G5 in SONET mode, such as insertion of B1, AIS, and RDI.The Rx SONET block error

detection circuitry is also functional and the data stream can be monitored for errors via ORCAstra or for channel

AC, by using the FPGA output pins shown in Figure 3.

AUTO_TOH mode can also be disabled.When disabled, allTOH bytes present in the SONET frame will be passed

through theTx SONET block untouched.The SONET scrambler/descrambler may be enabled or disabled when not

using AUTO_TOH mode.

Note:When using the SONET scrambler, the first DINxx_FP that is provided will start the scrambler.A new location

of the DINxx_FP will not restart the scrambler with this new position.A SOFT_RESET or hard reset must be issued

to restart the scrambler with the new DINxx_FP position.

Technical Support Assistance

Hotline: 1-800-LATTICE (North America)

+1-408-826-6002 (Outside North America)

Internet: www.latticesemi.com