100n

C

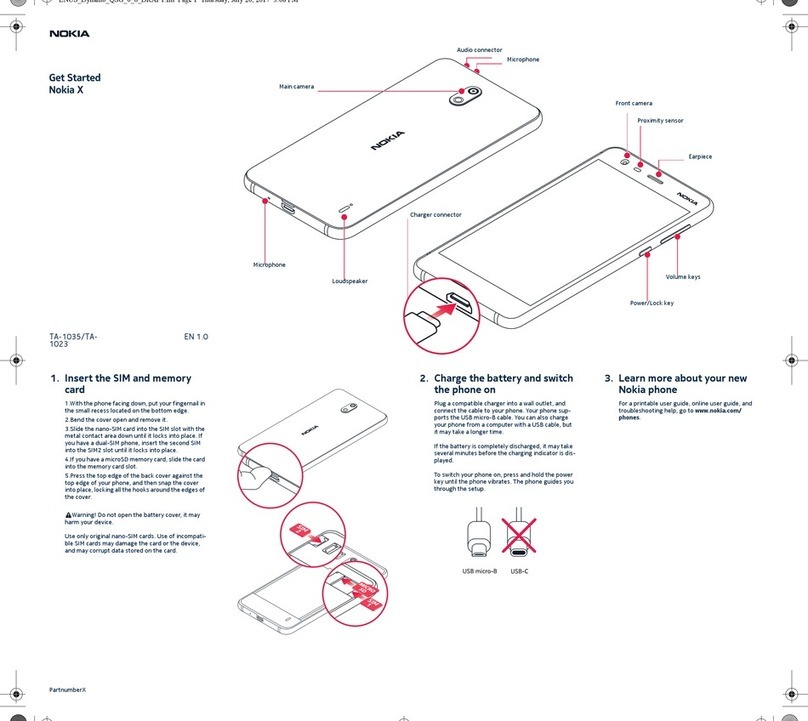

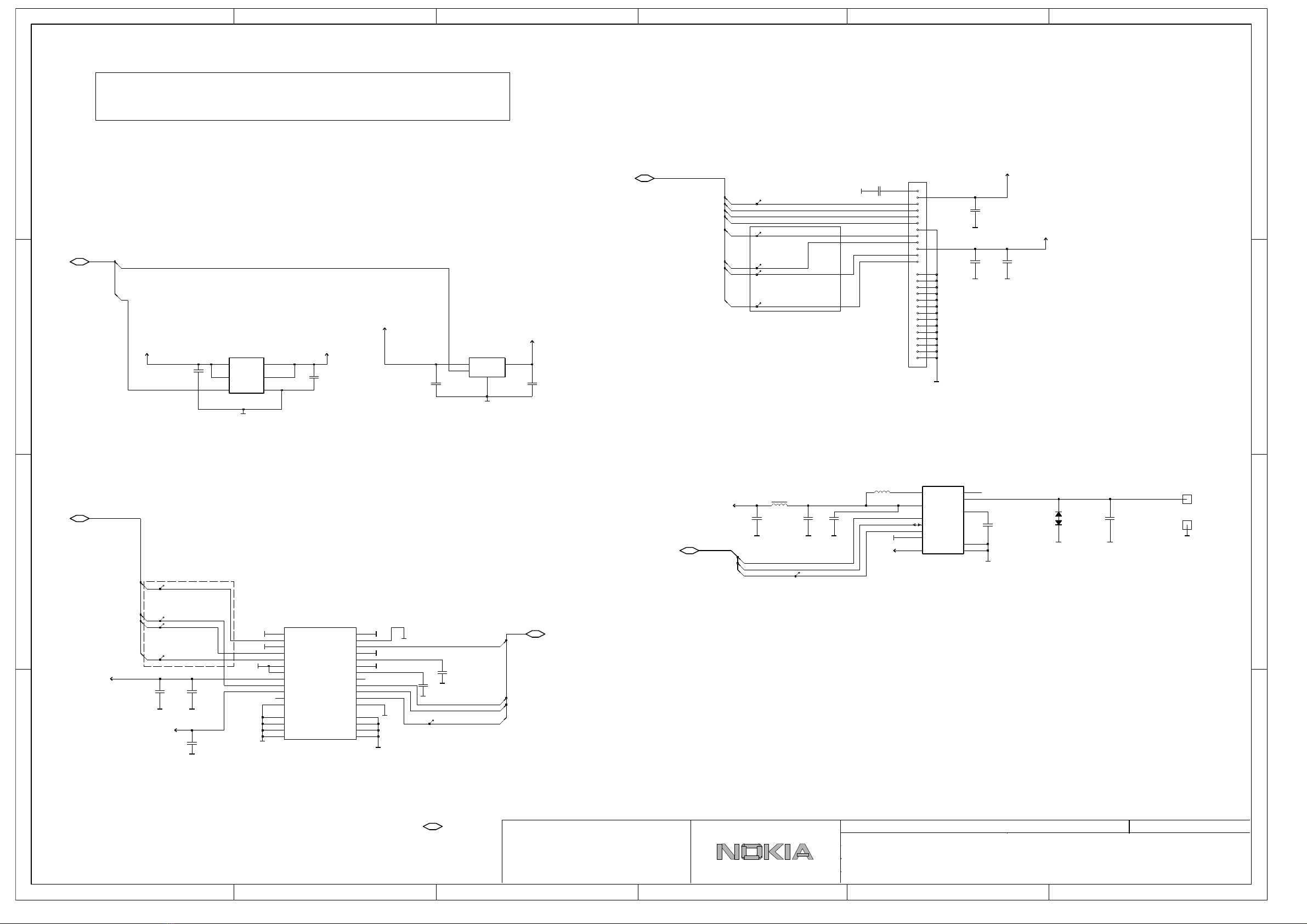

Bypass for CPU

0402

6

C2806 and C2807 combined to one 0203

0402

0402

Shared audioClk (Rapu-Gazoo-digimic) needs termination resistors in the beginning of each trace.

A

0203/2

6

100n

Bypass for CPU

100n

Shield DISPC_PCLK trace from every direction in order to avoid crosstalk injected to it.

Shield MMC Clk trace from every direction in order to avoid crosstalk injected to it.

0201

D

Termination place close to RAPU

Termination place close to RAPU

0203/2

0203/1

5

100n

A

Shield Sleepclock trace from evey direction in order to avoid crosstalk injected to it.

Resistor values to be defined with simulations.

0203/2

0203/1

B

1

REMOVE RAPU 2.0

100n

Bypass for CPU

0203/1

CCP IF: Differential interface -> match lenghts and maintain symmetry even with clk and data..

B

3

Signal integrity instructions:

C

2

5

D

Gazoo 2.0 sleepClk: Place T-filter (47R-33pF-47R) near Gazoo before dividing traces to other components.

0203/2

Bypass for CPU

Termination place close to RAPU

Internal LDO

Bypass for CPU

100n

C2841 and C2803 combined to one 0203

MemCard IF between Rapu-Gazoo: Traces should as short as possible and have good ground reference.

Preferred routing layers, 4 and 5. No stubs allowed. Minimum trace widht for achiving 100Ohm impedance.

Layout instructions:

0203/1

0201

32

4

41

Shield audioClk trace from every direction in order to avoid crosstalk injected to it.

Bypass for CPU

Shield SysClk192 trace from every direction in order to avoid crosstalk injected to it.

SysClk192: termination needed if is used or shared in design.

ETM Interface: traces should be as short as possible and have steady impedance, shield signal for preventing crosstalk.

47R

R2802

100R

R2803

VIO

59

VIO

7

26

GND

7

39

RFClkP

RFClkN

VIO

2u2

2351104

C2830

73

3

4

5

VIO

4

5

14

65

34

7

Name RAPU_YAMA

This document is property of Nokia Corporation

THIS DRAWING CONTAINS PROPRIETARY AND CONFIDENTIAL INFORMATION.

UNAUTHORIZED REPRODUCTION OF THIS DRAWING IS NOT PERMITTED.

THIS DRAWING IS PROTECTED BY COPYRIGHT AS AN UNPUBLISHED WORK.

GND

VIO

Copyright (C) Nokia Corporation. All rights reserved.

Appr dd-mmm-yy

/2 100n1

C2820

2710205

36

17

GND

0

1

2

5

6

8

GND

10

VIO

49

64

54

VIO

6

VIO

1

5

6

18

16

17

0

1

0

VIO

2

20

5

77

32

VIO

GND

0

1

3

4

5

VIO

29

24

2

66

67

6

60

61

62

30

2710205

C2824

1 /2 100n

0

2

3

13

45

VIO

1

0

9

37

GND

28

4

R2804

1430006

3k3

9

6

50

51

57

56

GND

GND

22

3

7

5

0

GND

2

47

VIO

2

0

1

6

GND

6

GND

80

4

8

3

VRFC

VIO

1

35

5

76

3

4

VIO

GND

2

31

0

7

19

GND

4

/2 100n

27

44

86

87

82

2710205

C2810

1 /2 100n 2

C2810

2710205

0

11

VCORE

3

7

4

5

2

C2818

2710205

/2 100n

16

1

2710205

C2818

1 /2 100n

1

55

58

21

/2 100n

2710205

C2817

2

2u2

2351104

C2823

3

VIO

8

2

0

46

0

41

VIO

12

2

8

GND GND

47R

1419079

R2801

25

69

68

2710205

C2825

1 /2 100n

2

C2825

2 /2 100n

3

GND GND

0

GND

/2 100n

2710205

C2821

2

70

4

10

2

74

75

VIO

4

GND

3k3

1430006

R2805

11

11

10

2X100n

C2806

2710205

2 /2 100n

40

78

79

6

VIO

13

18p

2351107

C2826

GND

GND

VCORE

15

17

33

VIO

100n

1

2

GND

GND

2VCORE

C2801

2351017

0

1

/2 100n

2710205

C2814

2

1

15

16

GND GND

3

VIO

4

/2 100n1

C2814

2710205

9

C2824

2 /2 100n

1

1

10

/2 100n

2710205

C2811

2

0

VIO

7

8

42

11

VIO

20

GND

71

72

81

63

19

2X100n

2710205

C2806

1 /2 100n

2

6

2 /2 100n

C2841

2710205

2X100n

4

0

7

6

15

12

100n

16

2710205

7

VIO

9

2351017

C2800

T9 VDD5

VCCQ_POP2

U1

VSS U2

VSS U23

V23 VDDS3

Y12

VSS

VDD_POP12

Y23

/2 100n1

C2817

R8

R9 VDD5

T1 VDDS_1_4

T10

VDDRAM

VSS T11

T12 VDDSTACK

VSS T14

VDD

T15

T16

VSS

T2 VDDS1

VDDSTACK

T8

P2

P20

VSS

VDD5

P8

VSS P9

VSS R10

R11 VDD

VDD

R12

VDD

R13

R14 VDD

VDD

R15

R16 VDD

VDDSRAMOUT

M8 VDDSTACK

VDD5

M9

N15 VDD3

VSS N16

VDDS_1_1

N2

VDDS8

N21

N8 VDD5

P1 VCCQ_POP1

VSS P15

VSS P16

VSS

K8

K9

VSS

L1 VCC_POP3

L15

VSS

L16 VDD3

VSS L2

VDD5

L8

VSS L9

M1

VSSASUB

VDD3

M15

M16 VDD3

VSS

J14

VSS

J15 VDD3

J16 VDD3

VDD4

J8

VDDSTACK

J9

VDD_POP11

K1

K15

VSS

K16

VSS

VSS K2

VSS K22

VDDSTACK

VSS H2

VSS H22

H23 VDD_POP10

H7

VDDARX

H8

VSS

VDDA18V1 H9

J1

VDDATX

J10 VDD2

VDDSTACK

J11

VDD2

J12

J13

G1

VDDS9

G10

G16

VSS

VSS G8

H1 VDD_POP13

VSS H10

H11

VSS

VDDRAM H13

VDD3

H14

VDD3

H15

VSS H16

VDDS9

E1 VDD_POP9

VSSAPLLStack E2

VDDS12

E23

VDDAPLLStack E3

E5

VSSARX

F1

VDDA_ACS

VSSA_ACS F2

VSS F22

F23 VDD_POP8

VSSATX F3

VSS

VDD_POP7

C23

VSS C9

VDDS_1_3

D1

VDDA18V2 D12

D17

VSS

D18 VDDS5

D21

VSS

D22

VSENSE

D23 VDDS12

VDDS9

D8

D9

B7

VSS B8

VSS C10

C12 VDDS10

VSS C15

VSS C16

VSS C17

VDDS5

C18

C19

VSS

C21

VSS

VSS C22

AC8

VSS B10

VSS B12

VSS B15

VSS B18

VDDS6

B19

VSS B22

IFORCE B23

B3

VDDA

VSS B4

VSSA B5

VSS

VSS AB5

VSS AB8

AC11 VPP_POP

AC12

VSSRX2

AC13 VCC_POP1

AC15 VDDS7

AC4

VSS

AC5 VCCQ_POP4

AC6 VDDS2

AC7 VDDS2

VCC_POP2

VDDS_1_2

VCCQ_POP3

AA1

VSSRX1 AA14

AA15 VDDS7

VSS AA2

VSS AA20

VSS AA22

VDD_POP12

AA23

VSS AB10

VSS AB13

AB2

VSS

VDD_POP5

A15

A16 VDDS6

VDDS6

A17

A18 VDD_POP6

A21 VDDS6

VPP2

A22

A23 VPP1

A4 VDD_POP1

A5 VDDS4

VDD_POP2

A7

A9

/2 100n

D2800

RAPUYAMA_V1.11_PR_RITSA_BGA401

VDD_POP3

A10

A12 VDD_POP4

VSS A13

GND

2

C2816

2710205

040-056208

A2800

BASEBAND SHIELD

ASSEMBLY

1

VIO

1 /2 100n

2X100n

C2841

2710205

38

0

52

53

GND

VCORE

10

48

4

5

0

85

83

100n 2351017

C2802

GND

VRFC

2710205

C2820

2

21

/2 100n

R2806

27R

CE1MMX

FlsCS0X Y2

SDRAD14

Y22

9

6

1

R2807

100R

G22

J23 SDRCKE2

SDRXCS2

M23

V1

FlsWEX

FlsOEX V2

FlsADVX W1

FlsClk W2

W23 SDRAD13

Y1

NC

NC

AC23

B11 SDRCLKX

B16 NC

SDRLDQS2 B17

B20

SDRUDQS2

NC

C20

D2

SDRLDQS

NC

MMCClk

AB21

MMCCmd

NC

AB23

SDRAM_TEMP_SENSE AC14

AC19

MMCDa2

AC2 NC

MMCDa3 AC20

MMCDa0 AC21AC22

D2800

RAPUYAMA_V1.11_PR_RITSA_BGA401

SDRCLK

A11

A14 NC

SDRUDQS A6

FlsRstX AB11

FlsWaitX AB12

MMCDa1 AB19

AB20

R2808

84

14

GND

Y7

Y8

DISPC_DATA_LCD14

DISPC_DATA_LCD0 Y9

47R

Y18

GenIO69 Y19

GenIO75 Y20

Y21

GenIO13

GenIO25 Y3

Y4

DISPC_VSYNC

GenIO23 Y5

GenIO22 Y6

DISPC_DATA_LCD7

W4

GenIO3 Y10

GenIO0 Y11

Y13 CCPStrbP1

Y14 CCPStrbN1

CBusClk

Y15

ETMDa7 Y16

Y17

ETMDa5

ETMCtrl

V21

GenIO37

GenIO74 V22

V3

DISPC_DATA_LCD17

V4

DISPC_DATA_LCD11

GenIO11 W20

W21

GenIO46

W22

GenIO5

W3

DISPC_DATA_LCD13

DISPC_DATA_LCD16

U21 EarDataR

GenIO71 U22

U3

DISPC_DATA_LCD5

U4

GenIO8

U7

DISPC_DATA_LCD4

U8

DISPC_DATA_LCD10

DISPC_DATA_LCD15 U9

V20

GenIO39

U11

U12

GenIO43

CCPStrbN0

U13

CCPStrbP0

U14

I2C2SDA

U15

I2C2SCL

U16

U17

GenIO1

GenIO65 U20

T20

PMARP

T21

MicData

T22

T23

GenIO12

T3

GenIO26

T4

GenIO7

T7

GenIO17

GenIO2 U10

GenIO86

PMARN

R21

R22

GenIO48

EMInt1 R23

R3

GenIO14

GenIO20 R4

R7

GenIO18

T13

GenIO87

GenIO31 T17

EarDataL

GenIO35 P23

GenIO10 P3

P4 RFBusClk

P7

GenIO82

GenIO16 R1

GenIO33 R17

GenIO9 R2

GenIO47 R20

GenIO40 N23

RFBusEn1X

N3

RFBusDa

N4

N7

GenIO79

N9

GenIO50

P17

GenIO76

P21 SleepX

AudioClk0

P22

M22

DRXIP

M3

M4

GenIO84

M7

GenIO85

N1

GenIO81

N17

GenIO38

N20 PURX

GenIO73 N22

GenIO6

VREFP

L3

L4 VREFN

L7

GenIO83

M17

GenIO45

M2 DRXIN

SIMIOCtrl1

M20

SIMIODa1

M21

ULPIData2

GenIO57

RXIP

K3

K4 RXQP

K7 DRXQP

L17

GenIO58

SIMClk1

L20

L21 ULPIData4

L22

GenIO60

L23

J21

J22

GenIO34

TXQN

J3

RXQN

J4

DRXQN

J7

GenIO41 K17

ULPIClock

K20

K21 ULPIDir

K23

H17

H20 ULPIData3

ULPINxt

H21

H3 TXQP

IREF

H4

J17

GenIO55

J2 RXIN

ULPIData1

J20

ULPIData0

G20

G21

GenIO61

G23

GenIO52

G3 RFClkP

TXIN

G4

GenIO78 G7

RX2

G9

GenIO42 H12

GenIO62

TXIP

GenIO51 G11

G12 TxCClk

G13

GenIO29

G14

GenIO64

G15

GenIO36

G17

GenIO56

RFClkN

G2

ULPIStp

D6

SleepClk

D7

E20 ULPIData7

SMPSClk

E21

E22

GenIO59

E4 HissiData0N

ULPIData6

F20

ULPIData5

F21

F4

D14

GenIO27 D15

D16

GenIO28

D19

GenIO53

D20

GenIO54

D3 HissiClkP

D4 HissiData0P

HissiData1P

D5

EMU1

HissiData2P

C4

HissiData1N

C5

C6 EMU0

TXA

C7

C8 RXDa0

ExtSysClkReq

D10

D11

GenIO49

D13

GenIO32

TMAct

B6

GenIO68 B9

C1 TXP

C11

GenIO80

GenIO30 C13

C14 TxCDa

C2 HissiClkN

HissiData2N

C3

ETMClk

AC3

DISPC_ACBIAS

AC9

GenIO21

JTDI

B1

B13

GenIO4

GenIO63 B14

RXDATAClk

B2

GenIO67 B21

SysClk384

AB4

DISPC_DATA_LCD9 AB6

AB7

DISPC_DATA_LCD3

AB9 INT0

JTMS

AC1

AC10

GenIO72

AC16 SysClk192

AC17

ETMDa6

AC18

JTDO

CCPDaP1

AB14

CCPDaN1

AB15

ETMDa4 AB16

CBusEn1X

AB17

AB18

ETMDa1

AB22

GenIO77

AB3

DISPC_DATA_LCD1

DISPC_DATA_LCD6

AA21

DISPC_DATA_LCD12 AA3

AA4

GenIO19

AA5

DISPC_HSYNC

DISPC_DATA_LCD8 AA6

AA7

DISPC_PCLK

AA8

GenIO15

AA9

DISPC_DATA_LCD2

AB1

AA10

AA11

GenIO44

CCPDaP0

AA12

CCPDaN0

AA13

AA16 CBusDa

AA17

ETMDa2

ETMDa3 AA18

ETMDa0 AA19

GenIO70

D2800

RAPUYAMA_V1.11_PR_RITSA_BGA401

JTRSTn

A1

GenIO66 A19

A2 JTClk

A20 RX1

TXReset

A3

TxCDaCtrl

A8

GenIO24

1 /2 100n

13

12

8

GND GND

VRFC

2710205

C2816

18

5

GND

/2 100n1

C2811

2710205

VIOVIO

14

43

VIO

23

CCP0_DP

CCP0_DN

CCP1_DP

SDA2

CCP1_SN

CCP1_SP

CCP1_DN

Flash_Int

/2 100n1

C2821

2710205

I2C0(1:0)

CCP0_SN

SCL2

CCP0_SP

GENIO(99:0)

ETM(20:0)

VISSI(27:0)

EMINT(3:0)

SDRAM_AD(15:0)

SDRAM_DA(31:0)

EXTADDA(31:0)

SDRAM_CTRL(17:0)

SDRAM_BA(1:0)

MEMCONT(9:0)

INT_MMC(13:0)

RFCLK(1:0)

HISSI(8:0)

CCP(20:0)

USB(20:0)

I2C2(1:0)

DIG_AUDIO(8:0)

INT_SIM(5:0)

JTAG(6:0)

PUSL(15:0)

CBUS(3:0)

RFCTRL(11:0)

RFCONV(20:0)

TXC(2:0)

TXP

INT_MMC(13:0)

MEMCONT(9:0)

SDRAM_CTRL(17:0)