Contents

PHYTEC Messtechnik GmbH 2005 L-602e_3

Preface...........................................................................................................1

1 Introduction .........................................................................................3

1.1 Blockdiagram................................................................................6

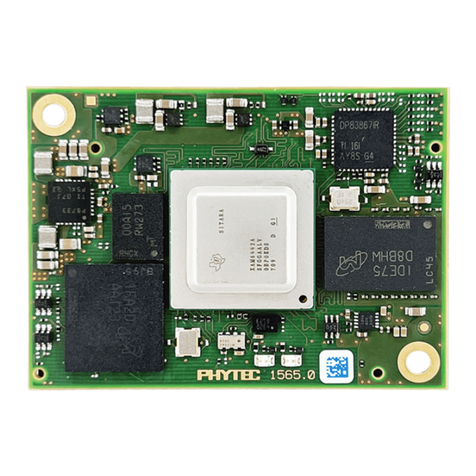

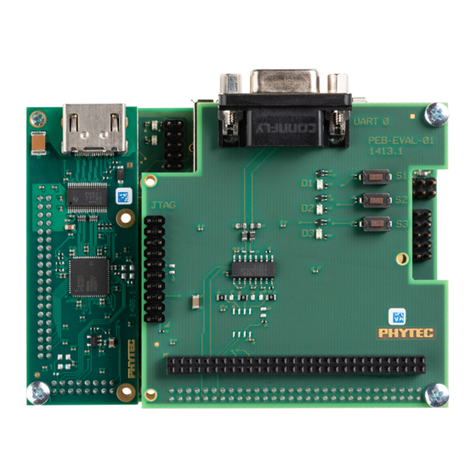

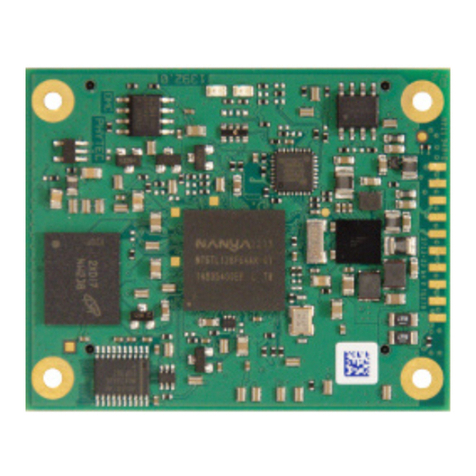

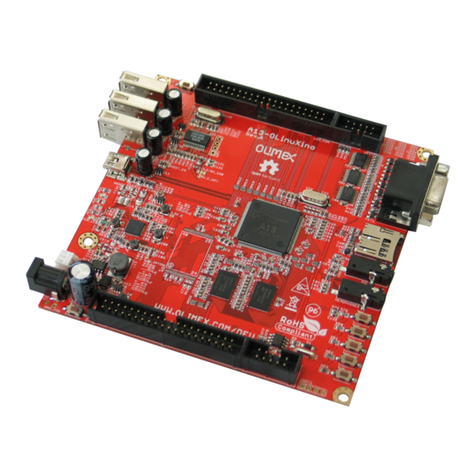

1.2 View of the phyCORE-P8xC51Mx2............................................6

2 Pin Description.....................................................................................7

3 Jumpers..............................................................................................13

3.1 J1 Internal or External Program Memory..................................16

3.2 J2, J3 Pin 1 and Pin 23 on U1....................................................16

3.3 J4 PLD Control..........................................................................17

3.4 J5, J6 RAM Selection................................................................17

3.5 J7 SRAM Supply Voltage..........................................................18

3.6 J8, J9 P3.0 and P3.1 as RxD0 and TxD0 Signals......................18

3.7 J10, J11 P4.0 and P4.1 as 2nd Serial Interface ...........................19

3.8 J12, J13 Pins X1F13 / X1E14 Configuration .............................19

3.9 J14 RS-485 Interface Control....................................................20

3.10 J15, J18 EEPROM Configuration .............................................20

3.11 J16, J17 Configuration of P1.6 and P1.7 for I2C Bus...............21

3.12 J19 RTC Interrupt......................................................................21

3.13 J20 Remote Download Source...................................................22

4 Memory Models.................................................................................23

4.1 Control Register 1.......................................................................25

4.2 Control Register 2.......................................................................28

5 Serial Interfaces.................................................................................30

5.1 RS-232 Interface.........................................................................30

5.2 RS-485 Interface.........................................................................30

6 Flash Memory (U7)............................................................................31

7 Serial EEPROM (U12)......................................................................33

8 Real-Time Clock RTC-8563/64 (U13)..............................................34

9 Reset Controller (U8)........................................................................35

10 Remote Supervisory Chip (U10) ......................................................36

11 Battery Buffer....................................................................................37

12 Technical Specifications....................................................................39

13 Hints for Handling the Module........................................................41